上次提到范紐曼五大單元CPU、Memory、I/O,也有提到指令週期,今天聊聊指令週期計算。

指令週期CPU執行指令流程中含Fetch->Decode->Execute->Write to Memory

這樣完整一個流程我們稱為一個週期cycle

週期時間衡量的方式有兩種

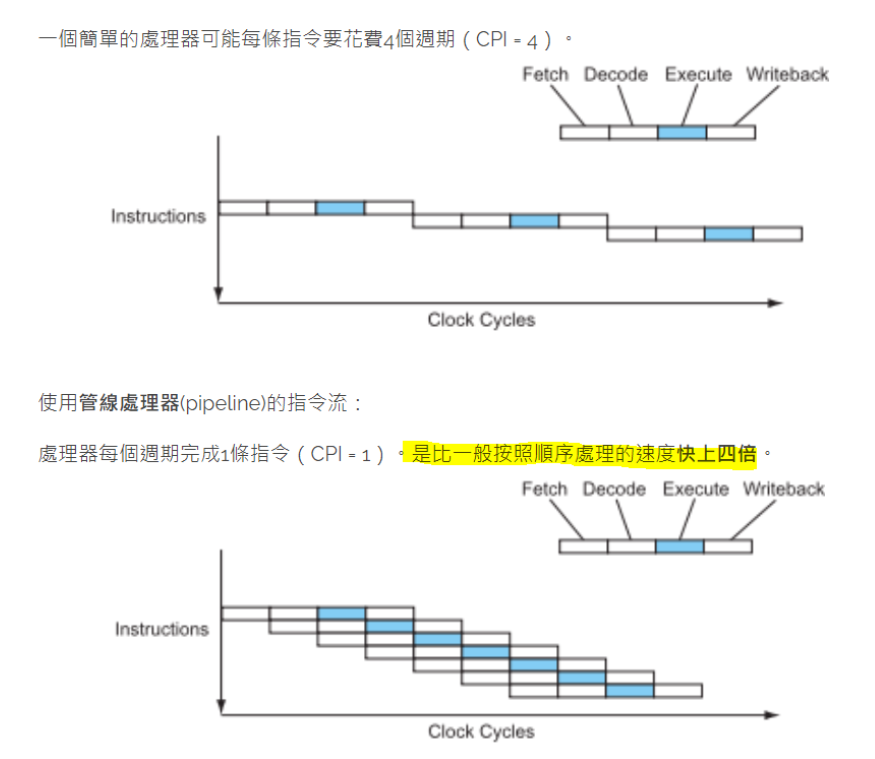

管線技術PipeLine依照范紐曼其中一個循序執行的原則,如果都要等一個指令走完一個指令週期才能執行下一個指令,會造成執行效能上的限制,因此管線技術出現。

藉由將不同的指令的不同週期同時執行,縮短整體的執行時間。

下一集來聊聊CPU架構和匯流排

QA時間

假設現在有三條指令,每條指令需要花6個clock cyle,使用管線技術會比沒有使用省多少clock cycle?

昨天答案:D

范紐曼瓶頸- 因為資料運算速度遠大於資料存取速度,當硬體效能不斷增加,資料傳輸會成為整體效能上的瓶頸。

而這瓶頸有一些解決方式

1. 提升匯流排DATA BUS的資料線,ex:32bit -> 64bit

2. 更換線材提升傳輸速度,ex:採用光纖(目前有線網路中最快的媒介)

分類會依照第一篇介紹的分類架構來進行

由於是將學習過程記錄下來,如果有任何錯誤歡迎糾正

以下參考連結在學習過程中覺得非常有幫助:

-WIKI

-台大線上課程