在數位電路設計裡,序列偵測器(Sequence Detector) 就像個「辨識器」,專門用來找特定的 0、1 序列,比如要偵測 "111"這段序列。序列偵測器在 數據傳輸、錯誤檢測、同步信號 等應用中非常常見,舉幾個例子來說:

• 數據傳輸:用來偵測 Start Bit,確保 UART、SPI、I2C 等協議正確讀取資料。

• 錯誤檢測:用來計算 1 的數量,判斷資料是否錯誤,應用於 Ethernet、Wi-Fi、SSD。

• 同步信號:偵測同步碼(Sync Pattern),確保發送端與接收端的時脈對齊,應用於 USB、PCIe、DDR 記憶體。

設計方式有兩種:

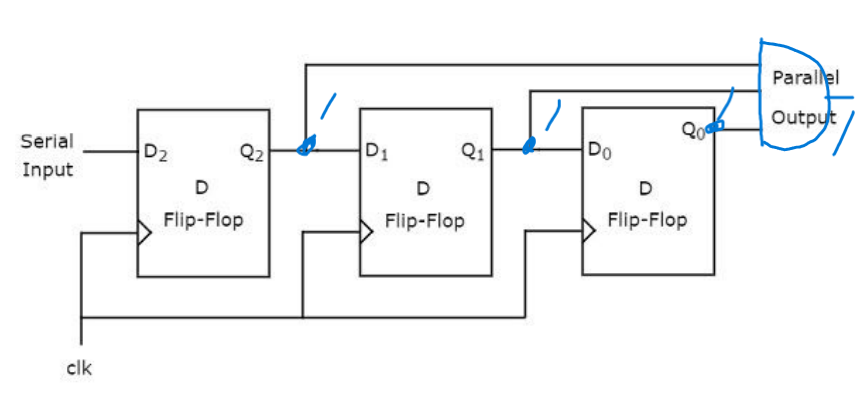

FSM(有限狀態機)法:用 D 觸發器 來記住輸入狀態,搭配邏輯閘 來決定下一步怎麼走。這種方法適合處理比較複雜的序列。移位暫存器法:把輸入數據存進 Shift Register,然後用邏輯閘比對,簡單直觀但比較不彈性。這次我們會用兩種方法,設計一個「看到三個連續的 1 就亮燈」的電路,利用 D 觸發器 + 邏輯閘 來讓它自動追蹤輸入的變化,準確偵測出 "111"!

FSM:

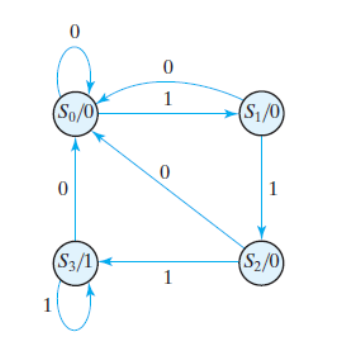

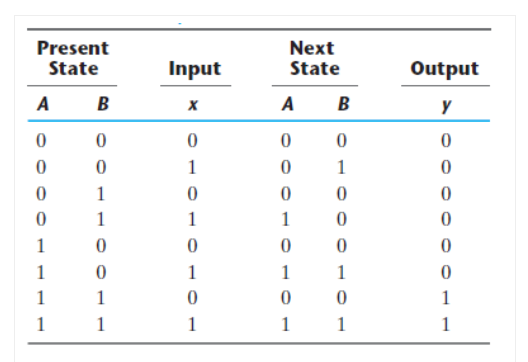

FSM 是一種狀態轉移的設計方法,用於需要精確控制狀態轉換的序列偵測。FSM 分為 Mealy 機和 Moore 機兩種,差異在於輸出是否直接被輸入影響。就是畫出state graph,然後化簡,得到電路

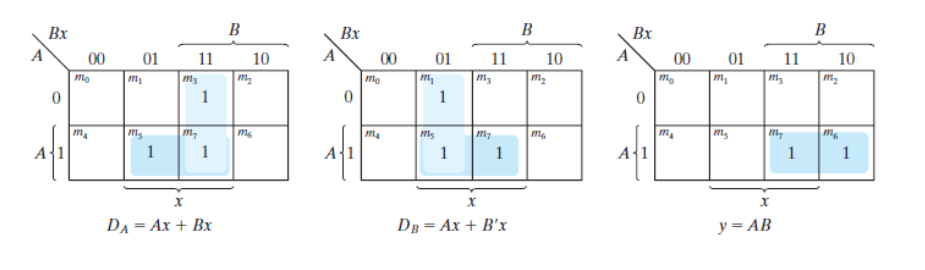

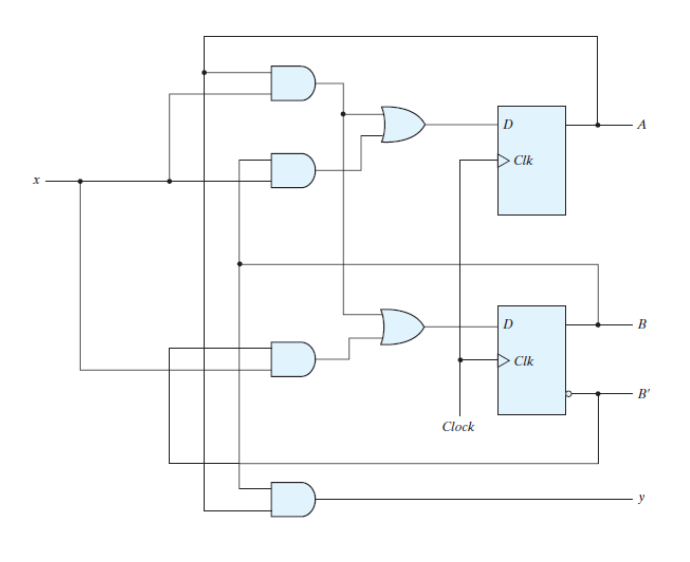

設計步驟:

最後根據化簡後的結果化出電路圖

輸入x不直接影響輸出y 所以是Moore machine

圖片參考此網站:

https://codestall.wordpress.com/2017/10/22/sequence-detection-of-3-1s-or-more-using-moore-model/

參考資料

https://www.geeksforgeeks.org/shift-registers-in-digital-logic/

http://mcatutorials.com/mca-tutorials-shift-registers.php

https://www.slideshare.net/slideshow/sequential-circuit-design2pdf/264820891