本文系統配置/拓撲(Topology):Raspberry Pi 3 (Grandmaster) → KSZ9477 (E2E TC) → AT32F403A (End Slave)

本文為中篇,接續上篇的環境建置與平台 bring-up,深入探討 PTP 系統的運行成果展示、時間同步精度驗證、以及常見問題與除錯技巧。本文將幫助讀者理解 PTP 系統的運行機制,掌握時間同步精度的量測方法,並學會系統除錯與優化技巧。

文章系列說明:

- 上篇:環境建置與平台 Bring-up(硬體連接、軟體初始化、平台啟動)

- 中篇(本文):成果展示與驗證(運行成果、精度驗證、除錯技巧)

- 下篇:系統整合與測試、兩點抓包驗證 TC CorrectionField(深入驗證、工程實作)

關鍵特色:

適用讀者:

閱讀建議:建議依序閱讀上篇 → 中篇(本文)→ 下篇,以獲得完整的 PTP 系統實作與驗證知識。

在上篇中,我們完成了:

系統架構設計:

硬體配置:

軟體架構:

環境建置:

平台 Bring-up 成功:

上篇成果:AT32F403A + DM9058 平台已成功運行,PTP daemon 能在「網路就緒後」成功初始化。

本文(中篇)重點:深入分析 PTP 系統的運行成果,驗證時間同步精度,並提供除錯技巧。

下篇預告:下篇將深入探討系統整合與測試,特別是使用「兩點抓包」方法驗證 Transparent Clock 的 CorrectionField 累加機制,提供工程現場可直接照做的測試 SOP 與故障排除手冊。

上篇的目標很單純:把 AT32F403A + DM9058 平台跑起來,且 PTP daemon 能在「網路就緒後」成功初始化。以下是上篇達成的主要成果展示:

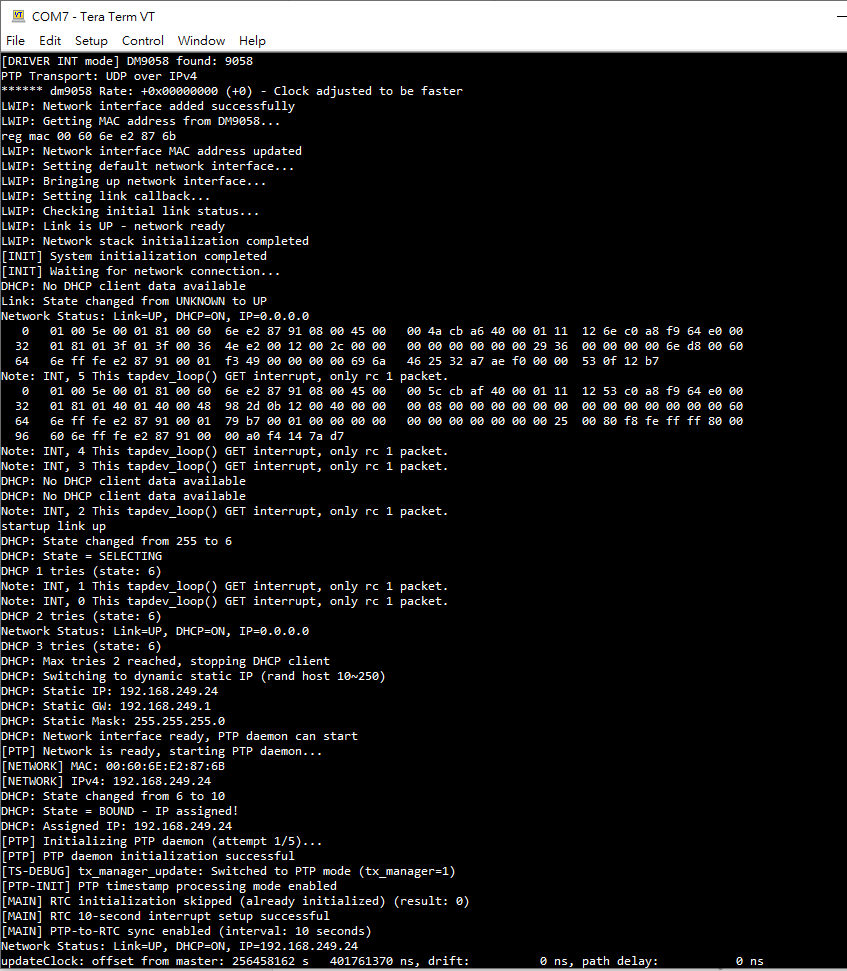

日誌解說:

此日誌展示了 AT32F403A + DM9058 平台的網路層初始化成功過程。關鍵訊息包括:

系統初始化階段:

[INIT] Configuring TMR6 for local_time updates:配置定時器用於系統時間更新LWIP: Initializing lwIP stack...:初始化 lwIP TCP/IP 協議棧LWIP: DHCP mode - setting IP addresses to 0.0.0.0:啟用 DHCP 模式,等待動態分配 IP硬體驅動初始化:

[SPI Instance] at32f403a_spi1_dma.c:SPI1 DMA 驅動初始化[SPI Pins] sck/mosi/miso/ pa5/pa7/pa6, cs/ pa15:SPI 接腳配置確認[DRIVER INT mode] AT32F403A INT Running...:外部中斷模式啟用[hal] at32f403a_spi1 'spi' Running 25Mhz...:SPI 時鐘設定為 25 MHzDM9058 晶片識別:

[DRIVER INT mode] DM9058 found: 9058:成功識別 DM9058 網路控制器PTP Transport: UDP over IPv4:PTP 協定使用 UDP/IPv4 傳輸網路介面就緒:

LWIP: Network interface added successfully:lwIP 網路介面添加成功reg mac 00 60 6e e2 87 6b:從 DM9058 讀取的 MAC 位址LWIP: Link is UP - network ready:關鍵訊息:實體層連線已建立(Link UP)Link: State changed from UNKNOWN to UP:連結狀態從未知變為已連線驗證要點:

日誌解說:

此日誌展示了 PTP daemon 成功初始化的過程,包含狀態機轉換和協定層啟動。關鍵訊息包括:

PTP Daemon 啟動條件檢查:

PTP 協定初始化:

PTPd_Init():PTP daemon 初始化函式被呼叫constants.h,經 bmc.c 的 initData() 寫入 ptpClock->defaultDS:

SLAVE_ONLY = TRUE:僅從時鐘模式DEFAULT_DELAY_MECHANISM = E2E:End-to-End 延遲機制DEFAULT_TWO_STEP_FLAG = FALSE → defaultDS.twoStepFlag:啟用 One-Step 模式(時間戳直接嵌入 Sync 訊息)PTP 狀態機轉換:

BMC(Best Master Clock)演算法:

clockClass、priority1、priority2 等參數驗證要點:

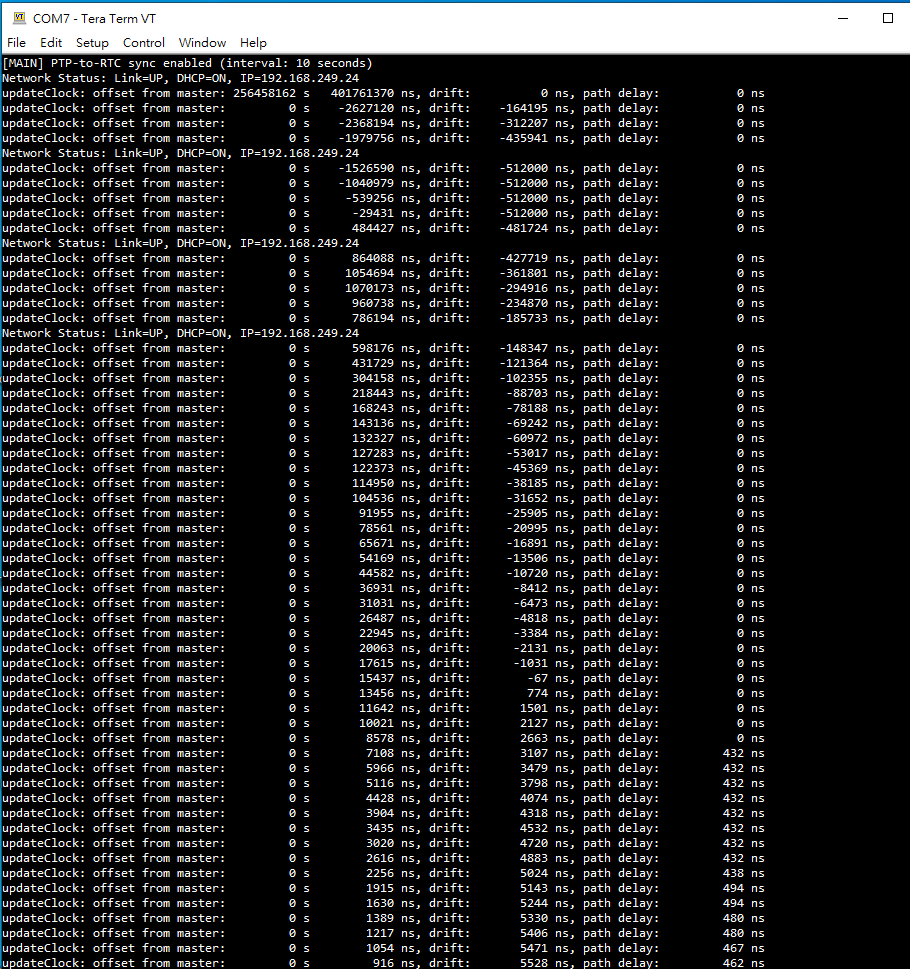

日誌解說:

此日誌展示了 PTP 系統正常運行時的周期性輸出,包含時間偏移量(Offset)和平均路徑延遲(Mean Path Delay)的計算結果。關鍵訊息包括:

周期性同步訊息交換:

時間偏移量(Offset)計算:

Offset = (t2 - t1 - CF_sync) - Mean_Path_Delay

平均路徑延遲(Mean Path Delay)計算:

Mean_Path_Delay = [(t2 - t1 - CF_sync) + (t4 - t3 - CF_delay)] / 2

日誌輸出格式:

updateClock: offset from master: 0 s -125 ns, drift: -82599 ns, path delay: 2340 ns

sync_interval 設定)輸出一次Clock Servo 控制迴路:

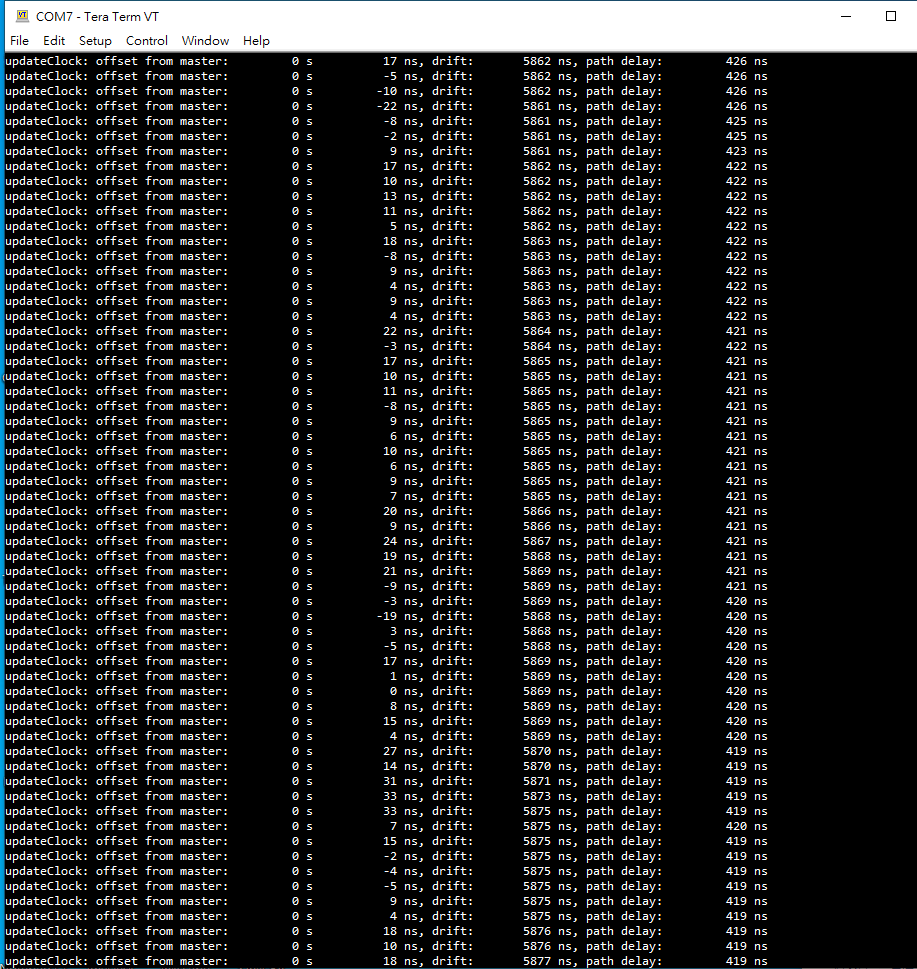

同步品質指標:

驗證要點:

PTP 系統的同步精度主要體現在 Offset 的收斂速度和最終穩定性上。

典型收斂過程:

初始階段(0-10 秒):

收斂階段(10-60 秒):

穩定階段(60 秒後):

理想同步精度指標:

PI 控制器參數調整:

PTP daemon 的 Clock Servo 使用 PI 控制器,主要參數包括:

調校建議:

注意:PI 控制器參數通常在 PTPd 的

servo.c中配置,建議參考 PTPd 文件進行調整。

問題 1:Link UP 但無法取得 IP

症狀:

LWIP: Link is UP - network ready

DHCP: No DHCP client data available

(長時間無 IP 分配)

可能原因:

除錯步驟:

問題 2:無法收到 PTP 封包

症狀:

可能原因:

除錯步驟:

ptp4l 正在運行問題 3:收到封包但協定無反應

症狀:

可能原因:

除錯步驟:

dep/net.c 中的 UDP bind 是否成功devif_ptp.c)問題 4:時間戳記不準確

症狀:

可能原因:

除錯步驟:

dm9058_ptp.c)dm9058_ptptime_gettime())dep/net.c)問題 5:系統運行一段時間後失同步

症狀:

可能原因:

除錯步驟:

測試場景:

驗證要點:

測試結果分析:

測試方法:

驗證要點:

測試場景:

驗證指標:

中篇的目標,是幫助讀者深入理解 PTP 系統的運行機制,掌握時間同步精度的量測方法,並學會系統除錯與優化技巧:

到這一步,您已經掌握了完整的 PTP 時間同步系統實作與驗證流程,能夠:

下一步建議:

在下篇中,我們將深入探討:

系統整合與測試:

兩點抓包驗證 TC CorrectionField(⭐ 下篇核心):

工程實作導向的驗證方法:

下篇將幫助您:

下篇定位:工程實作導向(可重現、可量化、可除錯),使用「兩點抓包」證明

correctionField在路徑中被累加。

| 中文 | 英文 | 縮寫 | 說明 |

|---|---|---|---|

| 拓撲 | Topology | - | 網路設備的連接結構 |

| 精確時間協定 | Precision Time Protocol | PTP | IEEE 1588 標準 |

| 透明時鐘 | Transparent Clock | TC | 修正網路延遲的中間設備 |

| 修正欄位 | Correction Field | CF | PTP 訊息中累加延遲的欄位 |

| 駐留時間 | Residence Time | - | 訊息在 TC 內部的停留時間 |

| 主時鐘 | Grandmaster | GM | 提供時間源的 PTP Master |

| 從時鐘 | Slave Clock | - | 同步到 Master 的設備 |

| 時間戳記 | Timestamp | - | 精確的時間記錄 |

| 偏移量 | Offset | - | Slave 與 Master 的時間差 |

| 單步模式 | One-Step | - | 時間戳記直接嵌入 Sync 訊息 |

| 端對端 | End-to-End | E2E | 延遲測量機制 |

| 比例積分控制器 | Proportional-Integral Controller | PI | 用於時鐘調整的控制迴路 |

SC0101_AT32F407_437_PTP_Daemon_V2.0.0.zip(本專案以其 PTP daemon 整合架構為基礎,移植到 AT32F403A 平台)SC0101_AT32F407_437_PTP_Daemon_V2.0.0.zip(移植基礎)dm9058_edriver_v1.6.1a

上一篇:AT32F403A + DM9058 實現高精度 PTP 時間同步(上篇):環境建置與平台 Bring-up