系列文章 : 使用 Verilog 實作 in-order CPU

forwarding unit 負責

相關程式碼

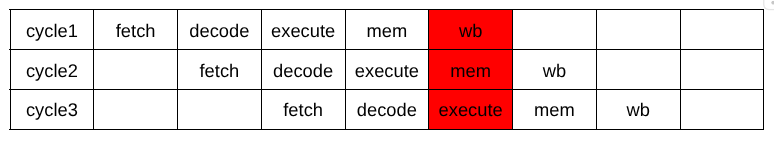

以上圖為例,總共有 3 個 instruction,分別是 cycle1, cycle2, 以及 cycle3

假設目前我們在上圖紅色框框的時間點。

可以怎麼樣進行 forwarding 呢 ?

mem-stage forward 資訊給 cycle3 的 ex-stagewb-stage forward 資訊給 cycle3 的 ex-stage介紹 forwarding 會用到的幾個訊號

cycle3 的 rscycle3 的 rtcycle2 這個 instruction 有沒有想要寫入 registercycle2 這個 instruction 想寫入的 register 是哪一個 ?cycle1 這個 instruction 有沒有想要寫入 registercycle1 這個 instruction 想寫入的 register 是哪一個 ?以下是 forwarding 條件的虛擬碼

forward_1_o = 0;

if (mem_regwrite_i == true && mem_regdst_i == ex_rs_i) {

forward_1_o = 1;

} else if (wb_regwrite_i == true && wb_regdst_i == ex_rs_i) {

forward_1_o = 2;

}

forward_2_o = 0;

if (mem_regwrite_i == true && mem_regdst_i == ex_rt_i) {

forward_1_o = 1;

} else if (wb_regwrite_i == true && wb_regdst_i == ex_rt_i) {

forward_1_o = 2;

}

當 mem-stage 確定會需要寫入 regfile,且寫入的 regfile 跟 ex_rs_i/ex_rt_i 一樣,這表示 ex-stage 所取用的 ex_rs_i/ex_rt_i 已經太舊了。需要從 mem-stage 將 rs/rt 從 mem-stage forward 過來。

wb-stage 的 forward 也是異曲同工之妙,但是優先度比 mem-stage 還低。

當 mem-stage 跟 wb-stage 都被偵測出可以進行 forwarding,我們會優先選擇 mem-stage 的資料,因為 mem-stage ( cycle2 ) 的資料比 wb-stage ( cycle1 ) 更新。

介紹一個簡單的例子。

假設 :

r3, r1, r2

r3, r2

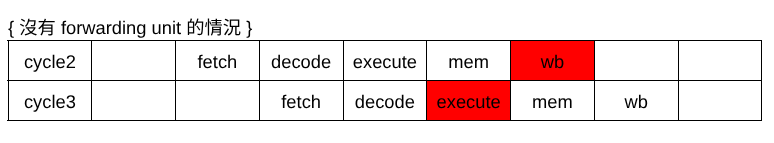

cycle3 會使用到 cycle2 寫入的 r3 register,沒有 forwarding unit 的話,會發生什麼事情 ?

因為 cycle2 要到 wb-stage 才會寫入 register,但是 cycle3 在 ex-stage 就需要使用 r3 了,這導致 ex-stage 會用到舊的 r3。

這就是一個簡單的 data hazard 的例子。

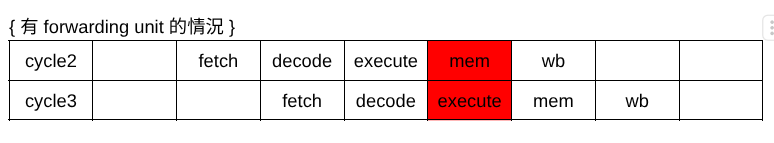

假如有 forwarding unit,cycle2 就可以在 mem-stage 把資訊 forward 給 ex-stage,讓 ex-stage 有最新的 r3。

再來介紹另外一個例子。

假設 :

r3, 4(r4)

r3, r2

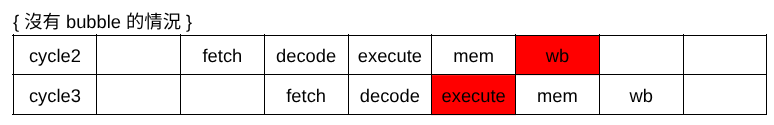

因為 lw 沒辦法在 mem-stage foward 資料給 ex-stage,最快最快也是要到 wb-stage 才有辦法 forward 給 ex-stage。

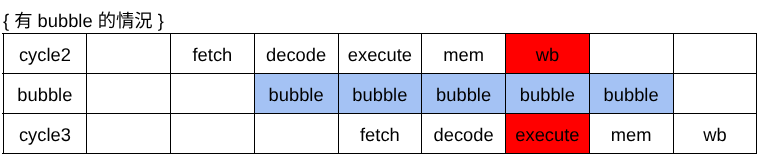

但是從上圖可以知道,wb-stage 沒辦法 forward 給 ex-stage,未來的資料 ( wb-stage ) 要怎麼傳遞給過去 ( ex-stage ) 呢 ? 當 cycle2 走到 wb-stage 時候,cycle3 也已經走到 mem-stage 了!

這也是一個 data hazard 的例子。

note : 為什麼不從 mem-stage,一拿到從 data-memory 的資料,就馬上 forward 給 ex-stage 呢 ? 我自己的想法 ( 不一定對 ) 是,一旦這樣做的話,那 mem-stage 跟 ex-stage 就變成一個大 stage 了,這樣就失去了切成 2 個 stage 的意義了。

從上圖可以知道,只要我們在 cycle2 跟 cycle3 中間插入一個 bubble,讓 cycle3 的 ex-stage 可以延後一個 cycle,這樣子 cycle2 的 wb-stage 就可以把資料 forward 給 cycle3 的 ex-stage了。

但是要怎麼偵測像這樣的 load-use data hazard ? 以及要怎麼樣才能在 pipeline 裡面插入一個 bubble ? 之後會寫一份 hazard detection 的筆記。