**請問需如何改善讀取到記憶體模組位址的pixel值,以及修改程式的結構(出現一直讀取不到指定位址與pixel數值),謝謝

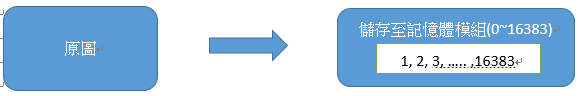

目前已經完成將一張影像128X128轉成pixel值後,放置到記憶體模組位址內

使用verilog語法撰寫,讀取記憶體模組位址內的pixel數值

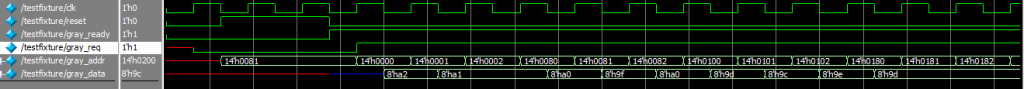

在modelsim模擬結果,波形輸出錯誤,以下為模擬結果

gray_addr(記憶體位址): 81(預設),0, 1, 2, 80, 81, 82, 100, 101, 102, 180, 181, 182, 200, 201, 202, 280, 281, 282

gray_data(pixel value): a2, a1, a1, a0, 9f, a0, 9d, 9c, 9e, 9d, 9d, 9c, 9c, 9d, 9d, 9c, 9d, 9b

程式:(以下是目前位址讀取錯誤的程式)

always@(posedge clk or posedge reset) begin

if(reset) begin

gray_addr <= 14'd129; //初始記憶體位址

end

//設定讀取記憶體模組內的piexl值

else if(gray_ready) begin

if(entries_filled == 4'd0) begin

//gray_addr <= gray_addr - 14'd129;

if(gray_addr[6] & gray_addr[5] & gray_addr[4] & gray_addr[3] & gray_addr[2] & gray_addr[1] & gray_addr[0]) begin

gray_addr <= gray_addr - 14'd127;

end

else begin

gray_addr <= gray_addr - 14'd129;

end

end

else if(entries_filled == 4'd1) begin

gray_addr = gray_addr + 14'd1;

end

else if(entries_filled == 4'd2) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd3) begin

gray_addr <= gray_addr + 14'd126;

end

else if(entries_filled == 4'd4) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd5) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd6) begin

gray_addr <= gray_addr + 14'd126;

end

else if(entries_filled == 4'd7) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd8) begin

gray_addr <= gray_addr + 14'd1;

end

end

else begin

gray_addr <= gray_addr;

end

end

input clk; // 時脈訊號

input reset; // 重置訊號

output [13:0]gray_addr; // 當為 HIGH 才可對 HOST 索取資料

output gray_req; // 灰階圖像資料

input gray_ready; // 灰階圖像位址

input [7:0] gray_data; // 當為 HIGH 表示向 HOST 索取資料

output finish; // 完成整張圖像後為 HIGH

//====================================================================

// macros

`define STATE_INPUT 2'd0

`define STATE_CAL 2'd1

`define STATE_OUTPUT 2'd2

`define STATE_IDLE 2'd3

//====================================================================

reg [13:0] gray_addr;

reg gray_req;

reg finish;

// 9 temp registers

reg [3:0] entries_filled;

//====================================================================

// FSM

/* FSM, Counters */

always@(posedge clk or posedge reset) begin

if(reset)

state <= `STATE_INPUT;

else

state <= nxt_state;

end

always@(*) begin

case(state)

`STATE_INPUT: begin

if(entries_filled == 4'd8)

nxt_state = `STATE_CAL;

else

nxt_state = `STATE_INPUT;

end

`STATE_CAL: begin

nxt_state = `STATE_OUTPUT;

end

`STATE_OUTPUT: begin

nxt_state = `STATE_INPUT;

end

`STATE_IDLE: begin

nxt_state = `STATE_IDLE;

end

default: nxt_state = `STATE_IDLE;

endcase

end

always@(posedge clk or posedge reset) begin

if(reset) begin

gray_req <= 1'b0;

end

else begin

if(gray_ready) begin

gray_req <= 1'b1;

end

else begin

gray_req <= 1'b0;

end

end

end

// 對應gray pixel位置

always@(posedge clk or posedge reset) begin

if(reset) begin

entries_filled <= 4'd0;

end

else if(gray_ready) begin

if(entries_filled == 4'd8) begin

if(gray_addr[6] & gray_addr[5] & gray_addr[4] & gray_addr[3] & gray_addr[2] & gray_addr[1] & gray_addr[0])

entries_filled <= 4'd0;

else

entries_filled <= 4'd6; //entries_filled <= 4'd6;

end

else begin

entries_filled <= entries_filled + 4'd1;

end

end

else begin

entries_filled <= entries_filled;

end

end

always@(posedge clk or posedge reset) begin

if(reset) begin

gray_addr <= 14'd129; //初始記憶體位址

end

//設定讀取記憶體模組內的piexl值

else if(gray_ready) begin

if(entries_filled == 4'd0) begin

//gray_addr <= gray_addr - 14'd129;

if(gray_addr[6] & gray_addr[5] & gray_addr[4] & gray_addr[3] & gray_addr[2] & gray_addr[1] & gray_addr[0]) begin

gray_addr <= gray_addr - 14'd127;

end

else begin

gray_addr <= gray_addr - 14'd129;

end

end

else if(entries_filled == 4'd1) begin

gray_addr = gray_addr + 14'd1;

end

else if(entries_filled == 4'd2) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd3) begin

gray_addr <= gray_addr + 14'd126;

end

else if(entries_filled == 4'd4) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd5) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd6) begin

gray_addr <= gray_addr + 14'd126;

end

else if(entries_filled == 4'd7) begin

gray_addr <= gray_addr + 14'd1;

end

else if(entries_filled == 4'd8) begin

gray_addr <= gray_addr + 14'd1;

end

end

else begin

gray_addr <= gray_addr;

end

end

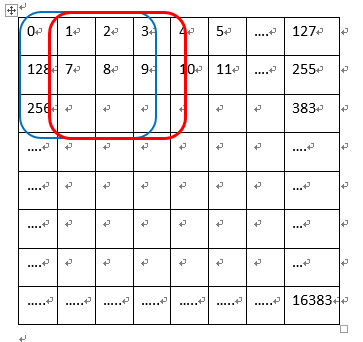

實際需要方法:

正確讀取記憶體模組的piexl數值後,以size 3X3為一個block,藍色區域第一次讀取到的piexl數值,紅色區域第二次讀取到的piexl數值,讀取順序為

藍色區域第一次 => 0,1,2,128,129,130,256,257,258 (此為記憶體模組位址)

紅色區域第二次 => 1,2,3,129,130,131,257,258,259 (此為記憶體模組位址)

時序表(記憶體模組位址):

0,1,2,128,129,130,256,257,258,1,2,3,129,130,131,257,258,259

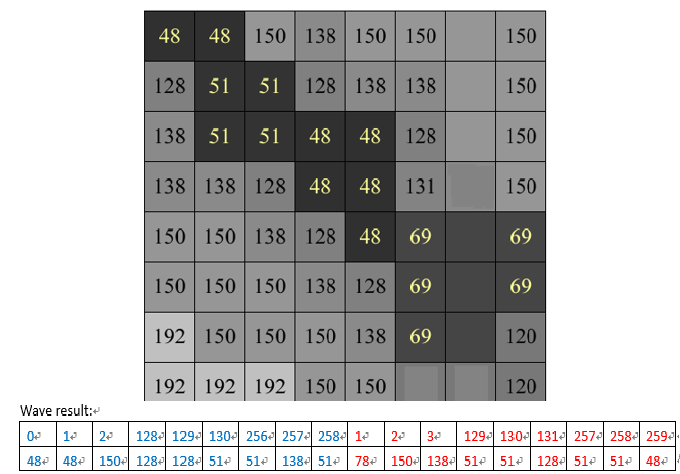

記憶體模組的piexl數值,對應到pixel對應為原圖piexl,產生時序會受到clk與reset影響,以下舉例結果(不考慮延遲情況):