如果希望 CPU 可以支持某一種功能運算,那就必須實現對應的硬體

在前一篇我們已經知道乘法器在硬體實現上的步驟

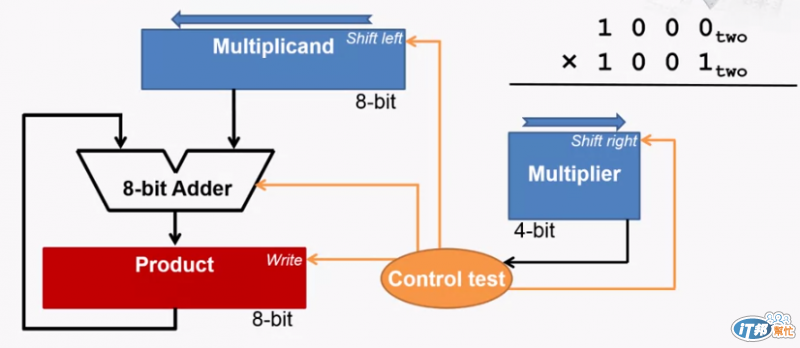

那現在就讓我們一起來看一下乘法器的具體電路實現

相較於加法器,乘法器的電路圖相對之下複雜許多

要實現一個四位元的乘法運算,需要兩個八位元的暫存器,分別儲存被乘數與乘積

乘數則會使用四位元的暫存器儲存,被乘數與乘數分別會依照控制信號指示左移或右移

另外還有一個八位元的加法器,根據控制信號進行加法運算

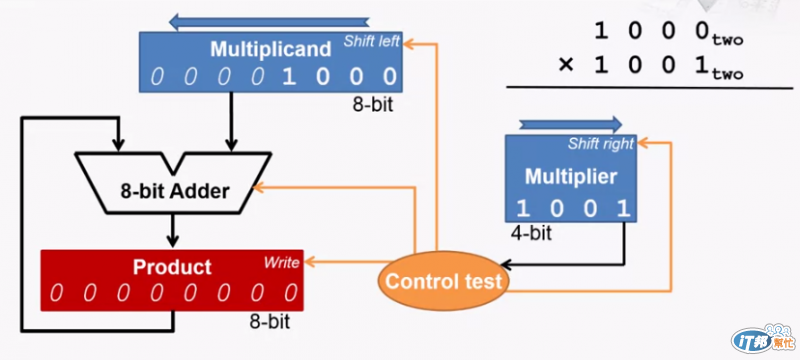

一開始會初始化乘數和被乘數,接著將乘積設置為零

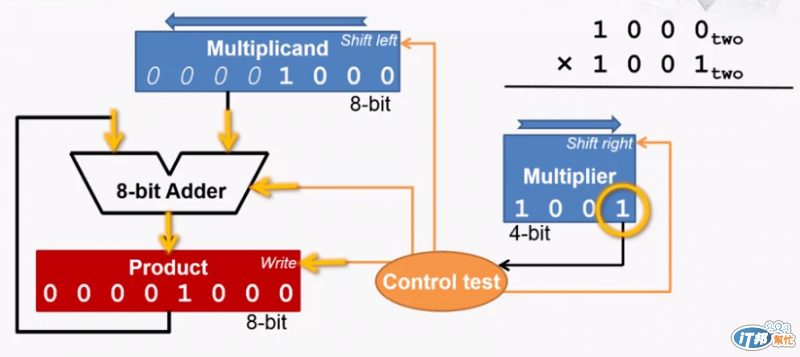

接著控制信號會檢查乘數的最低位元,目前為一

因此被乘數和乘積會進行加法,並且寫入乘積暫存器中

這樣就完成了第一輪的乘法運算,接下來控制信號會將被乘數左移,以及右移乘數,

因為對於硬體來說要記住下一個需要判讀的乘數是哪個位元,實作上會比較麻煩

而且一但使用過的乘數之後就沒有用了

所以我們可以將乘數右移每次只要判讀最低位元,這樣一來就可以減少硬體的複雜度

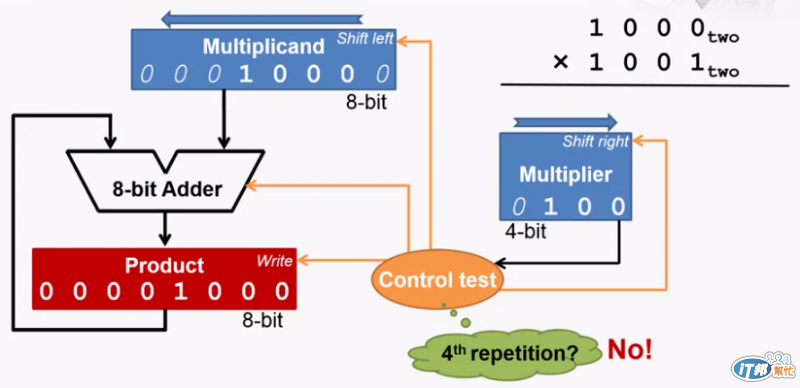

另外控制邏輯還會有一個簡單的計數器,來記錄目前是第幾輪的乘法

假設超過四輪,那運算當然就可以結束了

再依序執行以上步驟之後,當控制邏輯中的計數器發現已經是第四次,就表示完成了計算

此時在乘積暫存器中的就是結果了

我們也可以注意到此時乘數與被乘數中的數值雖然有進行了移位,但是卻沒有實際的意義

上圖就是擴展到 N 位乘法器時的通用步驟,只要有足夠的晶體管就可以構建出這個基本的乘法器

那和加法器相同,這個乘法器也有可以進行優化的部分,就留待明天來介紹~:)