鐵人賽首先要先知道過去有哪些 CSR,以及這些 CSR 所代表的意義,接著再來認識有新增了哪些 CSR。

前些日子有介紹了許多 CSR 可以先去觀看參考

DAY2

DAY3

midelegh、mieh、mvienh、mviph、miph 用於 RV32,以支援 64 個 interrupt。0~31 interrupt ID 使用 mideleg,而32~63 interrupt ID 使用 midelegh,每個 interrupt ID 佔用一個bit。

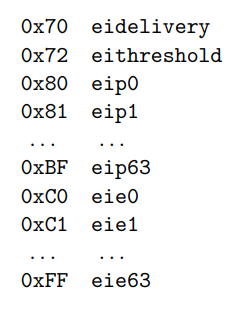

miselect 是一個 WARL 暫存器,根據實現的功能決定它支援的範圍,當未實現 IMSIC 時,miselect 的範圍為0~0x3F;當實現 IMSIC 時,miselect 的範圍為0~0xFF,miselect 範圍分配:

目前 0x00~0x2F 和 0x40~0x6F 是未指定是使用者使用,故不慎使用到會引發 illegal instruction exception。

通常,external interrupt 範圍為 0x70-0xFF,當在實現 IMSIC 時才有效;否則,當 miselect 在此範圍內時,嘗試 access mireg 也會觸發 illegal instruction exception。

miselect 會根據下圖的值,使 mireg 表示成不同意義的暫存器,譬如 miselect =0x80

,則可以再利用 mireg 對 eip0 做操作

這些 register 與 machine level register功能相匹配

下圖為 supervisor-level 新增的CSR

siselect 0x00~0xFF分配如下:

無論是否有實現 IMSIC ,為了實現最大相容性,siselect 建議支援 9 bit 範圍也就是 0x00~0x1FF。

目前 0x00~0x2F 和 0x40~0x6F 是未指定是使用者使用,故不慎使用到會引發 illegal instruction exception,或是在 0x70~0xFF 範圍內且未實現 IMSIC 時,嘗試access sireg 會造成 illegal instruction exception(除非在 VM(virtual machine)執行)。

如果 hart 有實現 hypervisor extension 則下圖列出 hypervisor 和 VS CSR 也會被添加

vsiselect, vsireg, vstopi 跟 supervisor CSRs 相似,並且在 VM 執行時替換這些 supervisor CSR。

不論是否有實現IMSIC,vsiselect 需要支援 9 bit 範圍0x00~0x1FF,當 vsiselcet 的最高有效位設為 1 時,這些值將指定為自定義使用。

下方是vsiselect 0x00~0x1FF範圍分配

當 vsiselect 的值為 inaccessible 範圍(0x0~0x06F),若從 M mode 或是 HS mode 嘗試 access vsireg,將會引起 illegal instruction exception,若從 VS mode 嘗試 access vsireg,則引起 virtual instruction exception。

當 hstatus 的 VGEIN 欄位為已實現的 guest external interrupt ID,且不為零時,才能 access external interrupt ( 0x70 至 0xFF)的 regitster 位置。如果 VGEIN 不是已實現的guest external interrupt(包括未實現 IMSIC 的情況),則所有非自定義的 vsiselect 值都指定為無法 access 的 register。

同樣地,當 hstatus.VGEIN 不是已實作的 guest external interrupt 的 ID 時,若在 M-mode 或 HS-mode 要 access vstopei 會引起 illegal instruction exception;若在 VS-mode 要存取 stopei 則會引起virtual instruction exception。

這章節主要介紹,hart 新增了哪些 CSR,基本三大模式 M、S、VS level,三種模式的 CSR 算大同小異的,有些介紹比較含糊的地方,在後面的章節有較完整的介紹,這邊大概知道有增加什麼 CSR 即可。

主要新增 *iselect 以及 *ireg,利用這兩個 CSR 來 access 各種暫存器

另外也補充相關 CSR 的指令用法,搭配過去既有的 CSR 會較有感覺,蠻多新增的 CSR 是過去 CSR 的擴充,主要填補 32~63 個interrupt的部份。

OK~我們明日將會介紹 IMSIC 它是甚麼?用途是甚麼?