我們要先來設計一個訊號,隨便寫一個吧

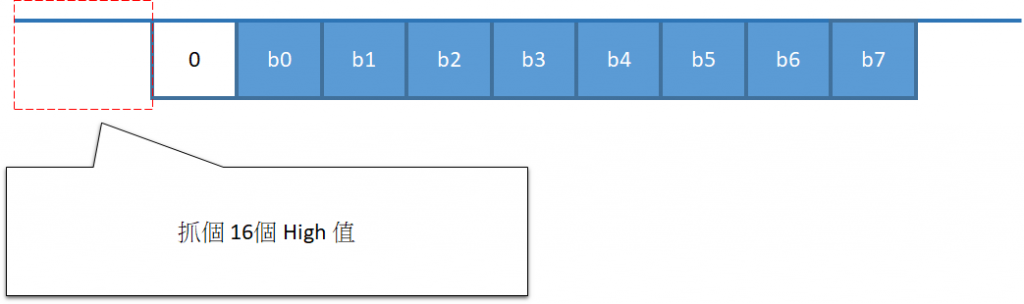

最前面為 16個 High,所以就是 16'b1111111111111111 簡化一點好了用 Hex寫 16'hffff

1.最前面為 16個 High 就是 16'hffff

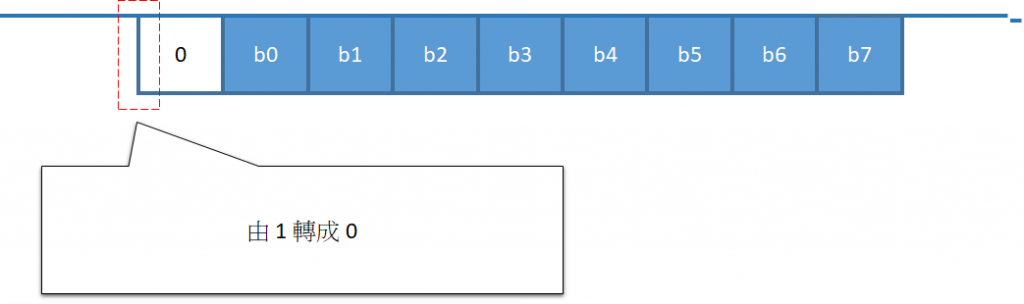

再來是 Start

2.Start 就是 2'b10

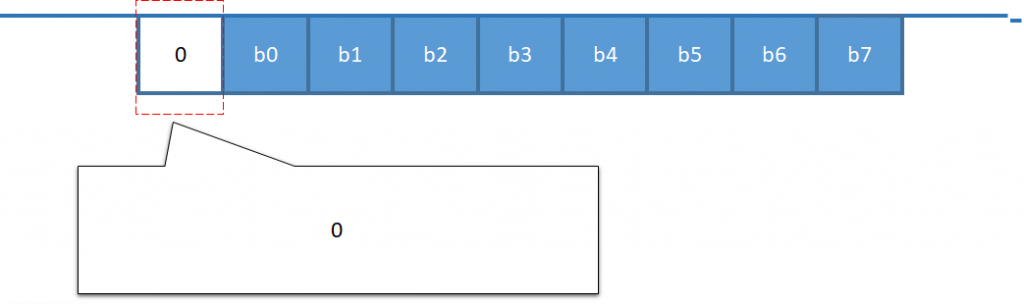

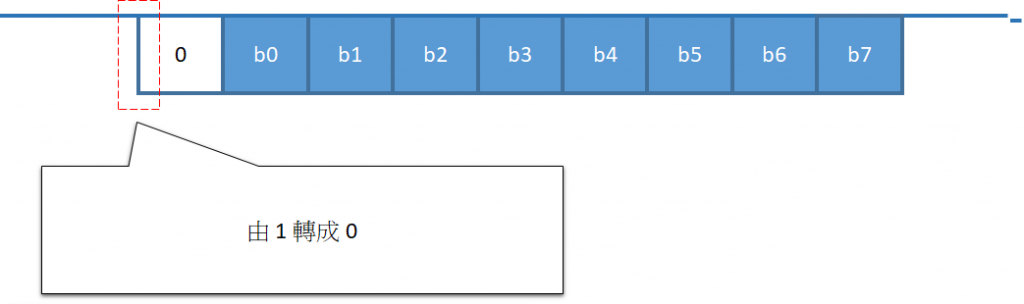

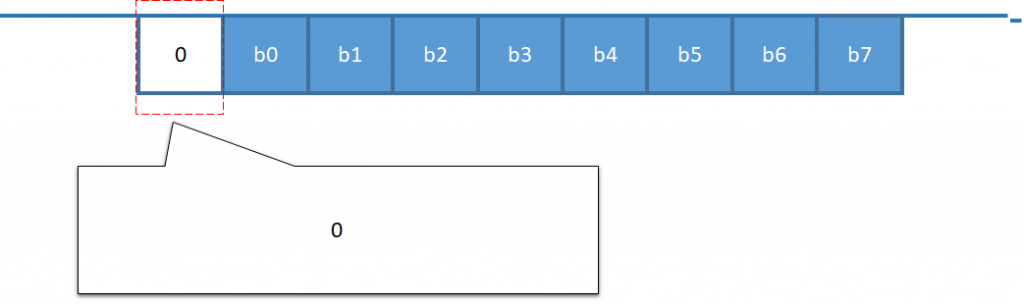

再來是 開始的 0

3.開始的 0 就是 1'b0

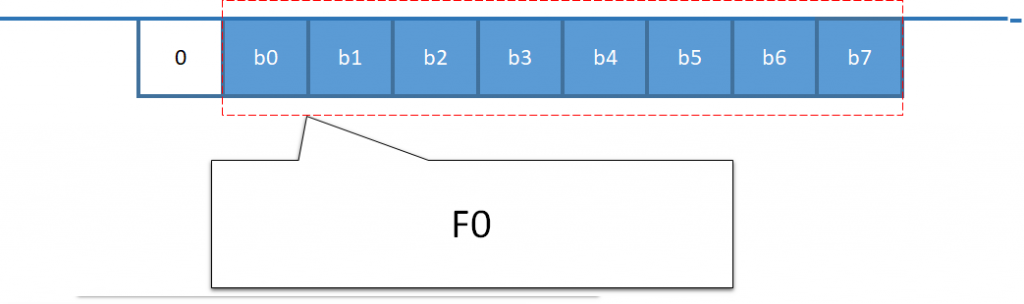

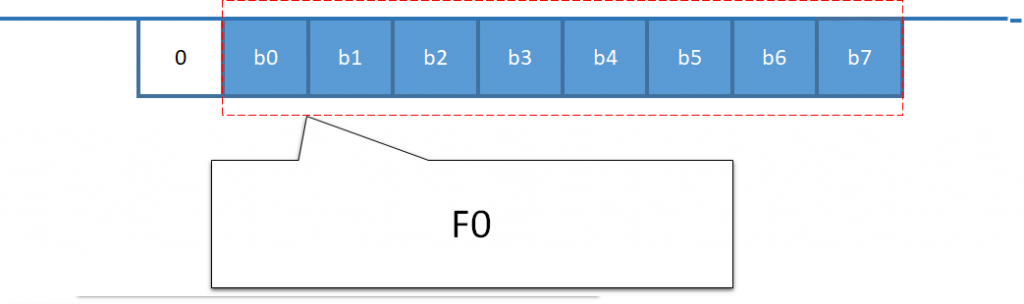

我們隨便想一下要輸入甚麼,那就輸入 F0好了

4.輸入 F0 就是 8'hF0

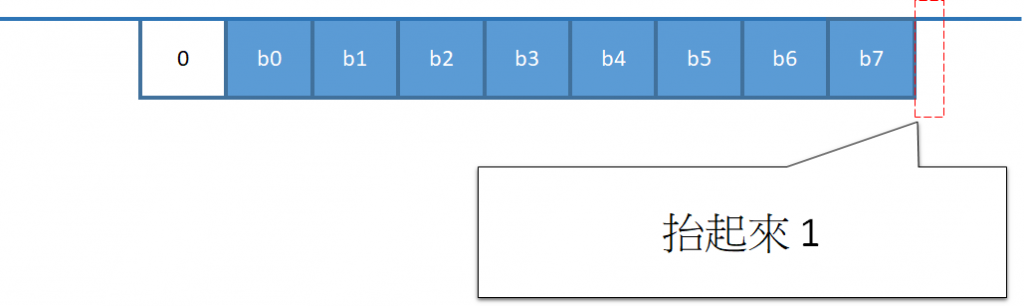

最後再把它抬起來,設成1

5.輸入 1 就是 1'b1

我們來組起來吧

再組起來前我們要先想,發送的位置,我們將 第0位做為發送

我們將 Data_Test_input的第0位接到Data_tb1,但是接線就要用到 Wire 所以步驟為

Data_tb1改為Wire

Data_Test_input的第0位接到Data_tb1

Data_tb1改為Wire

module tb1();

//Data_tb1改為Wire

Wire Data_tb1;

reg clk_tb1;

reg reset_tb1;

reg[???] Data_Test_input

module tb1();

//Data_tb1改為Wire

Wire Data_tb1;

reg clk_tb1;

reg reset_tb1;

reg[???] Data_Test_input

assign Data_tb1 = Data_Test_input[0];

我們設定 第0位做為發送,使用右移的方式,那要看看怎麼組出

所以步驟是:

1.最前面為 16個 High 就是 16'hffff

2.Start 就是 2'b10

3.開始的 0 就是 1'b0

4.輸入 F0 就是 8'hF0

5.輸入 1 就是 1'b1

1.簡化一點好了用 Hex寫 16'hffff

雖然是右移但是 一開始前面 16位都是1 所以沒差

Data_Test_input<={ ,16'hffff};

2.Start 就是 2'b10

但是右移所以是 2'b01 (右邊先輸出 2'b01 先輸出 0 在輸出1 就是 2'b10)

Data_Test_input<={ 2'b01,16'hffff};

3.開始的 0 就是 1'b0

Data_Test_input<={1'b0, 2'b01,16'hffff};

4.輸入 F0 就是 8'hF0

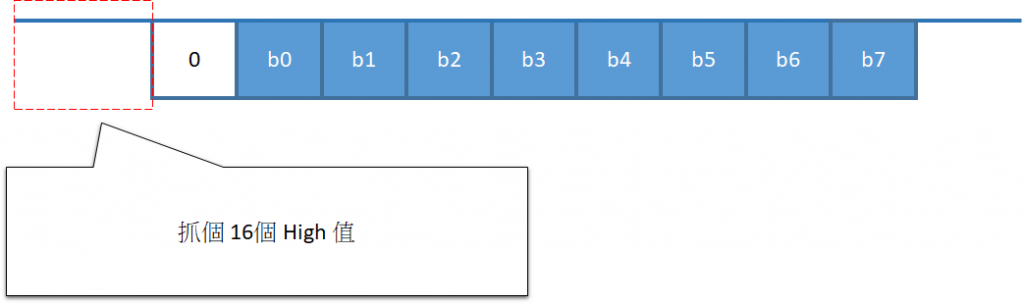

這時重新看一下這張圖

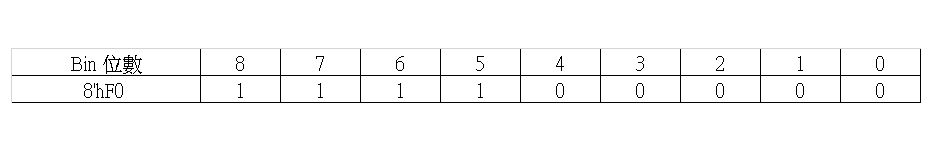

8'hF0 = {1,1,1,1,0,0,0,0}

先輸出 F0 的 b0 在輸出 Data_Test_input<={1'b0, 1'b0,2'b01,16'hffff};

在輸出 F0 的 b1 在輸出 Data_Test_input<={2'b00, 1'b0,2'b01,16'hffff};

先輸出 F0 的 b2 在輸出 Data_Test_input<={3'b000, 1'b0,2'b01,16'hffff};

在輸出 F0 的 b3 在輸出 Data_Test_input<={4'b0000, 1'b0,2'b01,16'hffff};

先輸出 F0 的 b4 在輸出 Data_Test_input<={5'b10000, 1'b0,2'b01,16'hffff};

在輸出 F0 的 b5 在輸出 Data_Test_input<={6'b110000, 1'b0,2'b01,16'hffff};

先輸出 F0 的 b6 在輸出 Data_Test_input<={7'b111000, 1'b0,2'b01,16'hffff};

在輸出 F0 的 b7 在輸出 Data_Test_input<={8'b11110000, 1'b0,2'b01,16'hffff};

5.輸入 1 就是 1'b1

Data_Test_input<={1'b1,8'b11110000, 1'b0,2'b01,16'hffff};

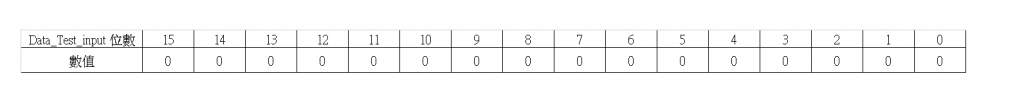

我們來算一下喔

1(1'b1)+8(8'b11110000)+1(1'b0)+2(2'b01)+16(16'hffff)

= 1 + 8 + 1 + 2 + 16 =28

reg[???] Data_Test_input → reg[27:0] Data_Test_input

好啦來初始化到 Data_Test_input

module tb1();

//Data_tb1改為Wire

Wire Data_tb1;

reg clk_tb1;

reg reset_tb1;

reg[27:0] Data_Test_input;

assign Data_tb1 = Data_Test_input[0];

Wire[7:0] Out_tb1;

Wire En_out_tb1;

Rs232_test1 Rs232_test_tb1(

.Data1(Data_tb1),.clk(clk_tb1),.reset1(reset_tb1),

.Out1(Out_tb1),.En_out(En_out_tb1)

);

initial begin

Data_tb1<=0; clk_tb1<=0; reset_tb1<=0;

//初始化Data_Test_input

Data_Test_input<={1'b1,8'b11110000, 1'b0,2'b01,16'hffff};

end

always #5 clk<=~clk;

always@(posedge clk) begin

if( Count_Test >= 287 ) begin

Count_Test<=0;

end

else begin

Count_Test <= Count_Test + 1 ;

end

if( Count_Test == 0 ) begin

??????????

end

end

endmodule

明天再來寫 如何右移輸出入 也就是 ??????????