[Nand Flash] 看懂VT圖 - 2 繪製VT圖

最後一篇要介紹的是VT圖的分析,通常papper或spec中出現VT圖都是用來展示實驗結果,或是解釋如何操作flash,並不會花篇幅解釋其中的意義,這邊會整理幾種Flash常見的狀況,並解釋其對應到VT圖上會有什麼變化,幫助大家了解波形跟Flash狀態之間的關聯,在看到實際的VT圖時,可以大概知道發生了什麼狀況。

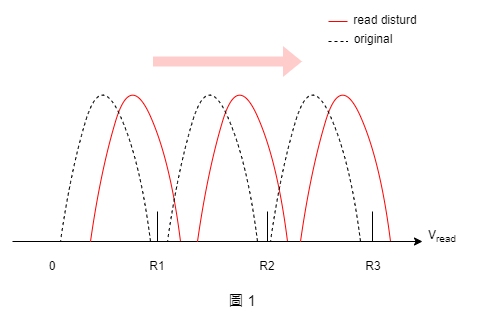

讀取干擾(read disturb)是同一個Cell被讀取許多次之後發生的錯誤,發生的原理可以參考闪存问题之Read Disturb,由於是多次讀取造成微寫入的效果,會使整個page的Vth變大,因此在VT圖上會看到所有波形往右偏移,如下圖1

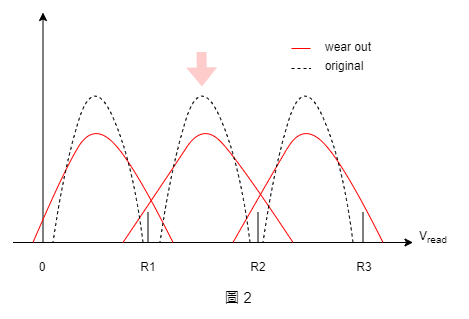

記憶損耗(memnroy wear out)會隨著cell PE cycle(program/erase cycle)增加逐漸產生,詳細說明可參考NAND flash wear-out 、Exploiting Memory Device Wear-Out Dynamics to Improve NAND Flash Memory System Performance,由於氧化層(絕緣層)損壞,會造成Vth無法被精準控制在read level的範圍內,對應到VT圖上的波形就會變矮、變胖,如圖2

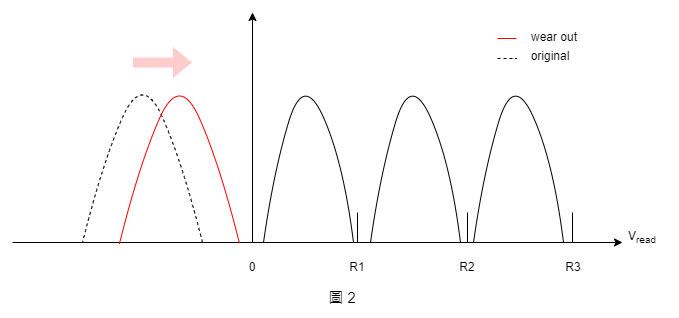

另外一個wear out的效應是絕緣層損壞造成erase時電子清不乾淨,因此VT圖上erase狀態的波形會往右移,如圖3

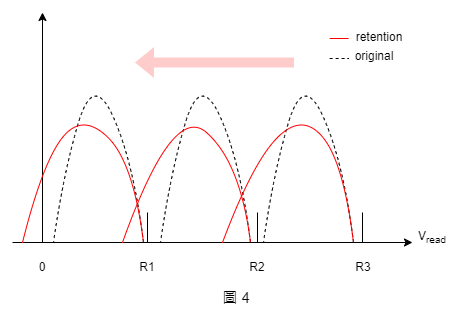

資料保留(data retention)也是Flash運作不可避免的特性,如同電子進入floating gate是機率性的,雖然機率很低,但時間久了電子還是會漸漸流失,詳細可參考FLASH DATA RETENTION。在VT圖的表現上是波形往左變寬,要注意不是整個往左偏移,參考圖4

前面都是波形變差的例子,最後舉一個變好的例子,two pass在QLC cell是很常見的program方式,原理是將flash充電的過程分階段執行,如此一來可以將Vth的範圍控制得更精準,NAND Flash Program Operation: One Shot VS. Two Pass中有詳細分解寫入的過程

總結來說,波形變化反映出的都是Vth範圍改變,以及cell內電子變多/變少的訊息,而在Flash製作及操作的各個環節都有可能造成影響,希望這幾篇整理可以幫助大家更了解VT圖的呈現的訊息。