今日的行程:

讀書室:09:30-11:00

今日的記錄:

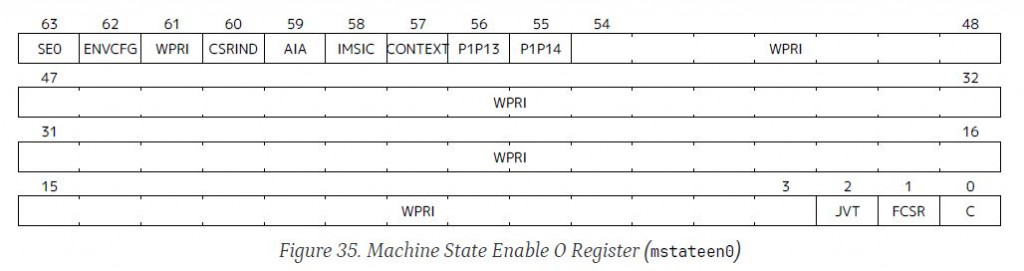

也是這幾天學到的 extension,有個很有趣的名字 S mstate en,是針對 state enable 這個 register 做的一些控制

stateen CSR 的每一個 bit 代表的是,更低層級的 mode 是否有權限存取這個 bit 代表的 extension 的狀態 (extension's state),和 counteren CSR 運作機制相同。直接上圖

On reset, all writable mstateen bits are initialized by the hardware to zeros.

If machine-level software changes these values,

it is responsible for initializing the corresponding writable bits of

the hstateen and sstateen CSRs to zeros too.

Software at each privilege level should set its respective stateen CSRs to

indicate the state it is prepared to allow less-privileged software to access.