系列文章 : 使用 Verilog 實作 in-order CPU

這邊的練習是來自陽明交通大學的計算機組織作業。

雖然我沒有上過陽明交通大學的計算機組織,但網路發達的年代,還是能找到計算機組織的作業內容,並練習,真是太棒了! 感謝好心人的分享。

https://github.com/Sea-n/NCTU-109B-Comp-Org/tree/master

這個練習基本上涵蓋計算機組織第四章( 處理器 )的一部分,學習如何實作一個有管道化 ( pipeline ) 的處理器。

https://www.tenlong.com.tw/products/9786267130681?list_name=trs-t

推薦可以買一本!放在家裡供奉著,也會感覺自己的智商提升了一點點。

我自己是買中文翻譯版本,因為比較便宜...

一千多元可不是一筆小數目! 學生的時候買不起,成為社畜之後終於可以狠下心的買下來了。

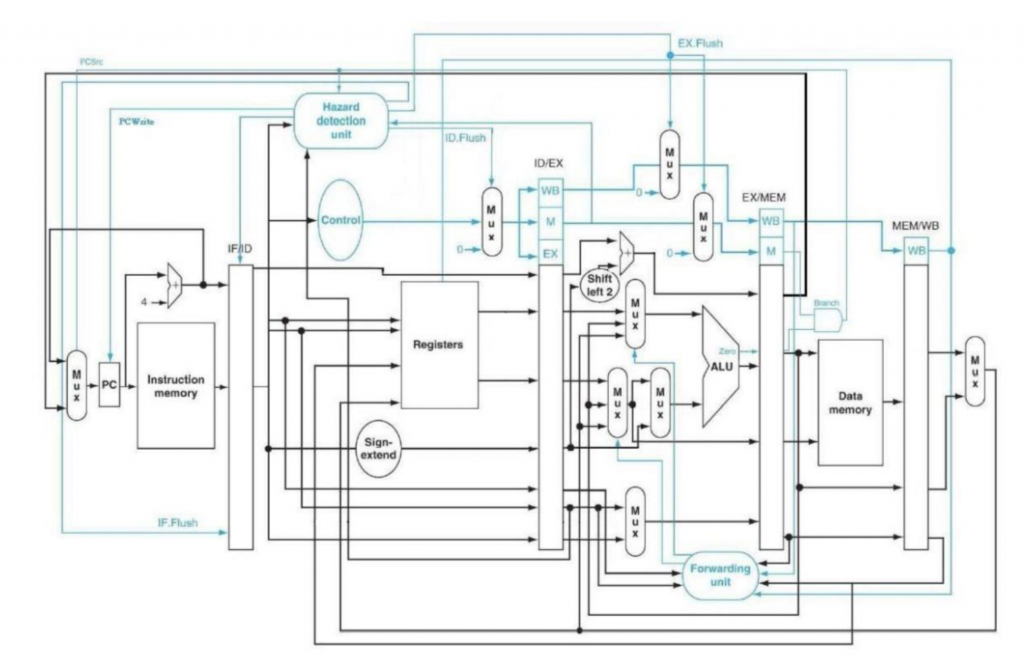

根據課本的內容,可以得知課本內的 pipeline 經典設計涵蓋了 5 個階段。

branch 嗎 ? 這個 instruction 會需要寫資料進記憶體嗎 ?這是這本聖經本所講述的是 5 stages pipeline ( 五階段管道 ) 經典設計。真正寫 verilog 的人當然可以自己設計 3 stages, 4 stages, 8 stages … 只是聖經本針對 5 stages pipeline 這個經典設計進行教學。

根據作業的要求

https://github.com/TommyWu-fdgkhdkgh/simple-mips/blob/main/spec.pdf

另外作業裡面,也有附設計圖,接下來就開始根據作業需求,以及作業提供的提示來實作這顆 CPU 吧!