系列文章 : 使用 Verilog 實作 in-order CPU

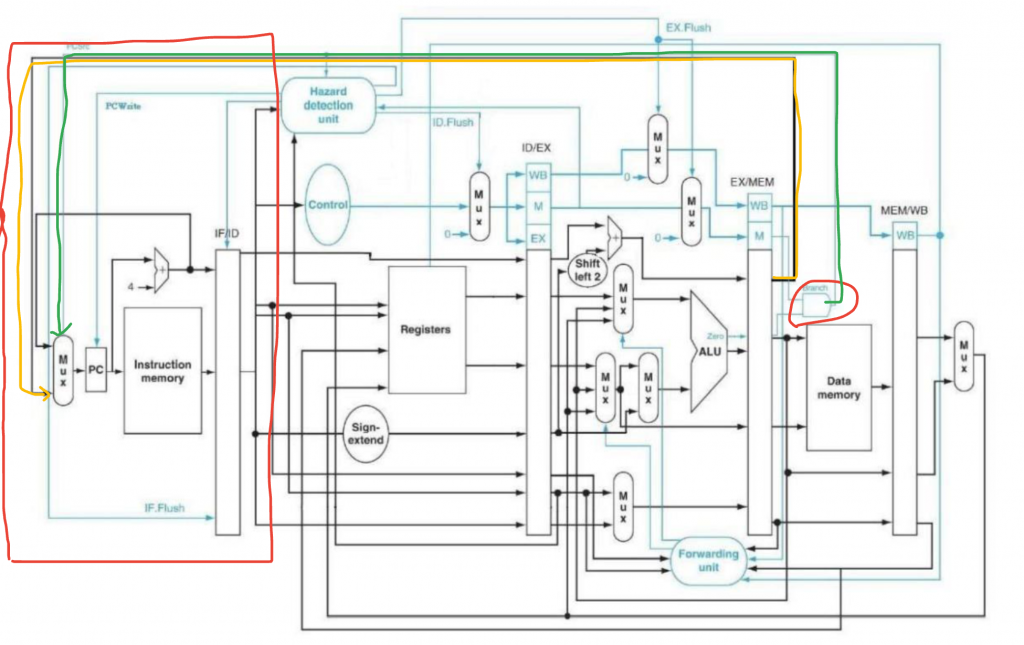

fetch-stage 會利用 pc 值,去跟 Inst_Mem 去要 instruction。

在 fetch 階段,會用到

相關程式碼

Program_Counter 提供 PC 值,也就是我們想要拿取 instruction 的位址。

e.g. pc == 4, 就從 Inst_Mem 裡拿出 offset 為 4 的 4 bytes 資料。

Program_Counter 會從 pc_in_i 訊號拿取下一個 cycle 的 pc 值,並在下一個 cycle 的時候,輸出該 pc 值。

當 stall 發生的時候,下一個 cycle 的 pc 值就不會發生變化,下一個 cycle 持續輸出原本的 pc 值。

例如說,當發生 load-use hazard 的時候,我們會需要把 fetch-stage 跟 decode-stage 暫停 ( stall ),讓 execute-stage/mem-stage/wb-stage 繼續往下走,並且在 execute-stage 插入一個 bubble ( nop )。

note : 為什麼會需要插入 bubble ( nop )

這時候 execute-stage 會空出來,我們需要插入一個不會改變 cpu 狀態的 nop 進去。

nop 簡單來說就是沒有任何效用的 instruction

當沒有任何的 branch 發生的時候,我們就順順的在下一個 cycle 執行當前 pc 值 + 4 的 instruction。

從一開始的設計圖可以了解到,mem-stage 會把

branch 發生時,要跳到的 PC 值 傳到 fetch stagebranch 是否會發生 傳到 fetch stage這個 mux 就是看 branch 會不會發生

reg [31:0] memory [0:31];

一個簡單的記憶體。 reg[31:0] 代表了每一個元素的大小是 32 bits,[0:31] 代表總共有 32 個元素

我們可以用 $readmemb("testcase.txt", memory); 把我們想運行的 instruction 載入到 Inst_Mem 裡面,並讓 CPU 可以取得 instruction

fetch-stage 跟 decode-stage 之間的 pipeline register。

當 fetch-stage 要把資料交給下一個 stage,也就是 decode-stage 處理的時候,會需要先把資料暫存在 pipeline register,因為 decode-stage 是在下一個 cycle 才能處理這些資料。

Pipeline_Reg_IF_ID 會傳遞下列資料給 decode-stage

從 fetch stage 就可以看到,一個 stage 不只乖乖地做自己的事情,也需要跟其他

單元進行合作。

以這個設計來說, fetch-stage 會跟下列的單元合作

program_counter 以及 pipeline_reg_if_id,讓 program_counter 跟 pipeline_reg_if_id 不發生變化 ( 停住 )。不透過 pipeline register, 也就是fetch stage 在同個 cycle 就會收到資料。