系列文章 : 使用 Verilog 實作 in-order CPU

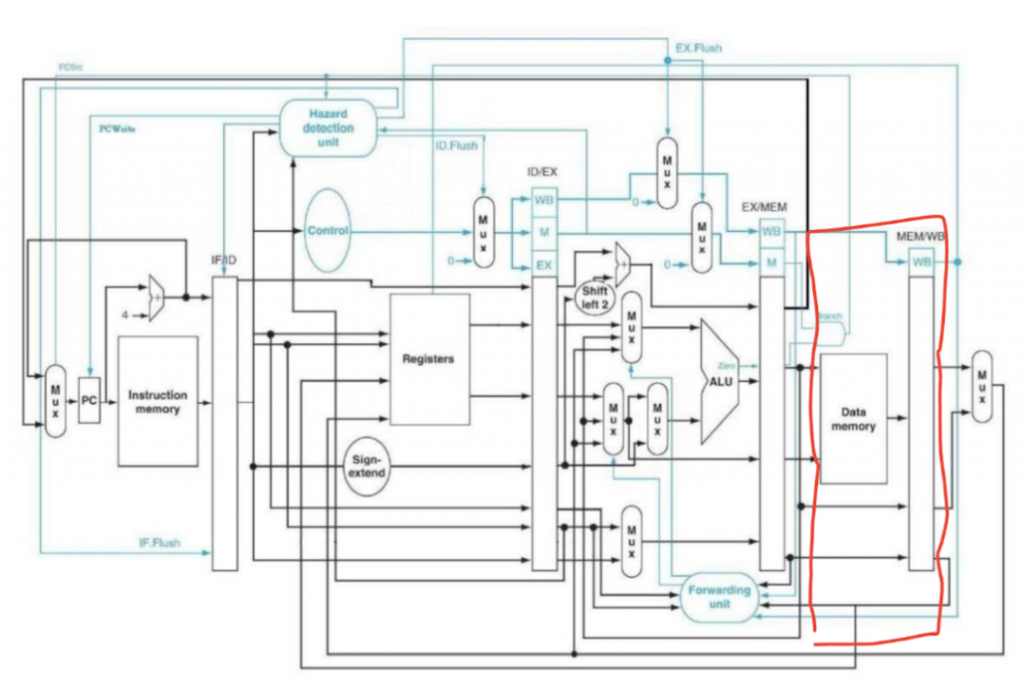

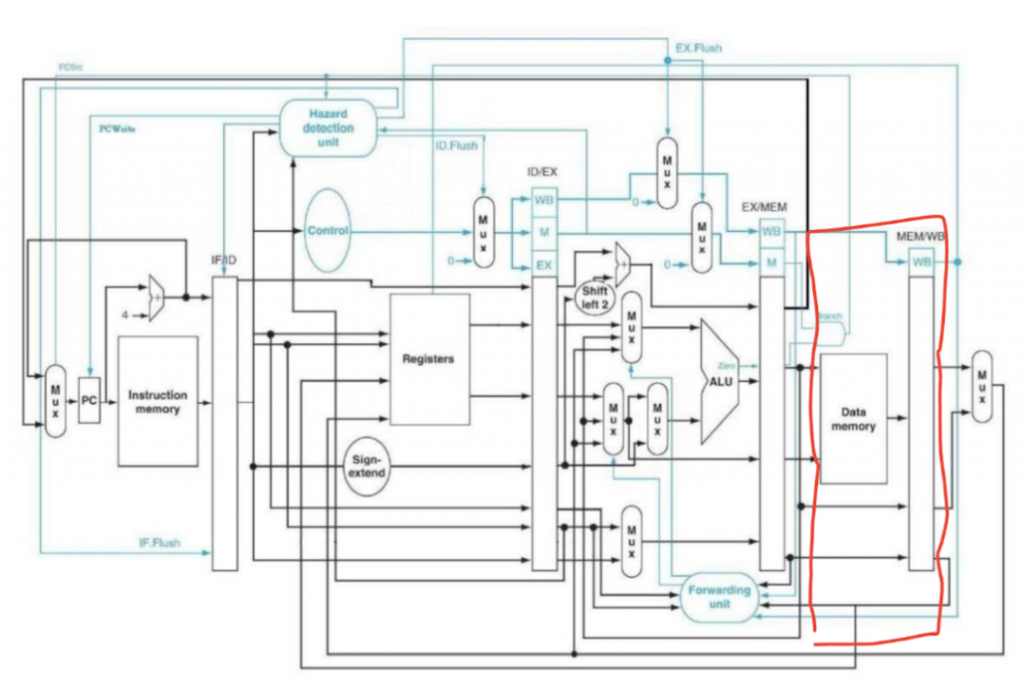

mem-stage

mem-stage 負責

- 決定是否該進行 branch,並且將這個結果傳遞到

fetch-stage 以及 hazard detection

- 對

data-memory 進行讀寫。

在 mem-stage 會用到

- Mux_4to1

- and gate

- Data_Memory

- Pipeline_Reg_MEM_WB

相關程式碼

Mux_4to1 #(.size(1)) mux_branch_type

d_branch_type_i 這個訊號代表了目前我們是使用哪一種 branch。

- 0 : branch equal ( beq )

- 兩值相減等於 0, 代表相同

-

alu_zero_i : 在 ALU 的時候,兩值相減得出是 0

- 1 : branch greater than ( bgt )

- 兩值相減後為正整數 ( 不可為 0 )

-

(~alu_result_i[31] & ~alu_zero_i) : 在 ALU 的時候,兩值相減後為正整數,且不為 0。

- 2 : branch greater than or equal ( bge )

- 兩值相減後不為負數 ( 可為 0 )

-

~alu_result_i[31] : 在 ALU 的時候,兩值相減 sign bit 為 0,代表結果為正整數。

- 3 : branch not equal ( bne )

- 兩值相減不等於 0

-

~alu_zero_i : 在 ALU 的時候,兩值相減不為 0,所以 alu_zero_i == 0。

and branch_and

- d_branch_i

- 這個 instruction 是否為 branch instruction

- mux_branch_type_o

- 這個 instruction 是否符合 branch 的條件

最後 branch_and_o 為 true 的話,表示這個 instruction 確定是 branch 且要跳的了。

Data_Memory data_mem

- alu_result_i

- 在 alu,會用 rs 跟 imm 計算出要放入 data-memory 的哪個位址 ( 也就是 address )

- regfile_2_i

- 想要放進 data-memory 的值 ( value )

- d_memread_i

- 從 decoder 那邊解析出的控制訊號,當為

true 的時候,就代表我們需要從 data-memory 讀取出資料。

- d_memwrite_i

- 從 decoder 那邊解析出的控制訊號,當為

true 的時候,就代表我們需要對 data-memory 寫入資料。

- data_mem_o

Pipeline_Reg_MEM_WB pipeline_reg_mem_wb

- Pipeline_Reg #(.size(1)) d_memtoreg

- 從 decoder 那邊解析出來的控制訊號

- 0 : 將 ALU 的結果存入 reg-file

- 1 : 將 data-memory 的結果存入 reg-file

- Pipeline_Reg #(.size(1)) d_regwrite

- 從 decoder 那邊解析出來的控制訊號

- 0 : 不需要對 reg-file 進行寫入

- 1 : 需要對 reg-file 進行寫入

- Pipeline_Reg #(.size(5)) regdst

- 假如我們需要對 reg-file 進行寫入,

regdst 代表寫入的位址 ( address )。因為 reg-file 裡面總共有 32 個 register,所以這個 address 的寬度為 5 ( 2 ** 5 = 32 )。

- Pipeline_Reg #(.size(32)) data_mem

- Pipeline_Reg #(.size(32)) alu_result