回到 Day21 的程式碼

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

reg[7:0] State1;

reg[7:0] Count_clk;

reg[7:0] Count_bin;

reg[7:0] Data_Previous1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Count_clk<=0;

Count_bin<=0;

Data_Previous1<=0ㄤ

State1 <=0;

end

else begin

Data_Previous1 <= Data1;

case (State1)

0:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

end

else begin

Count_clk <= Count_clk + 1;

end

if(Count_clk == 0 )begin

if(Data1==1)begin

Count_bin <= Count_bin+1;

end

else begin

Count_bin <= 0;

end

end

if(Count_bin== 15 )begin

State1 <= 1;

end

end

1:

begin

if(~Data_Previous1 & Data1 ) begin

State1 <= 2;

end

end

default:

begin

end

endcase

end

end

endmodule

我們加入第2狀態

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

reg[7:0] State1;

reg[7:0] Count_clk;

reg[7:0] Count_bin;

reg[7:0] Data_Previous1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Count_clk<=0;

Count_bin<=0;

Data_Previous1<=0ㄤ

State1 <=0;

end

else begin

Data_Previous1 <= Data1;

case (State1)

0:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

end

else begin

Count_clk <= Count_clk + 1;

end

if(Count_clk == 0 )begin

if(Data1==1)begin

Count_bin <= Count_bin+1;

end

else begin

Count_bin <= 0;

end

end

if(Count_bin== 15 )begin

State1 <= 1;

end

end

1:

begin

if(~Data_Previous1 & Data1 ) begin

State1 <= 2;

end

end

2:

begin

end

default:

begin

end

endcase

end

end

endmodule

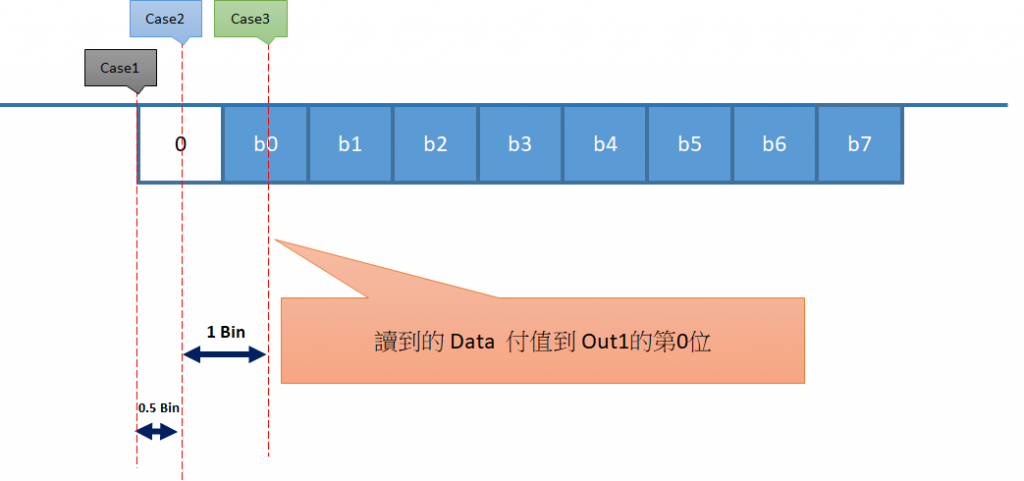

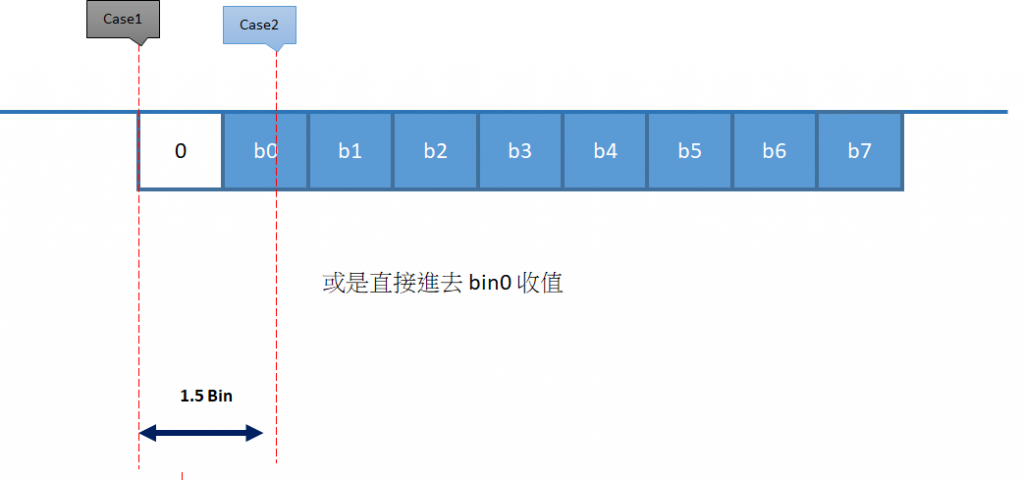

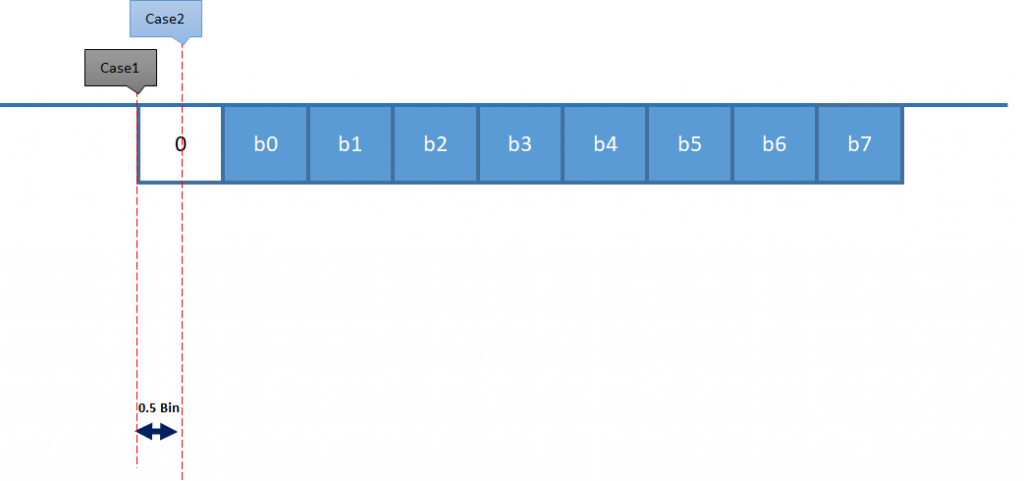

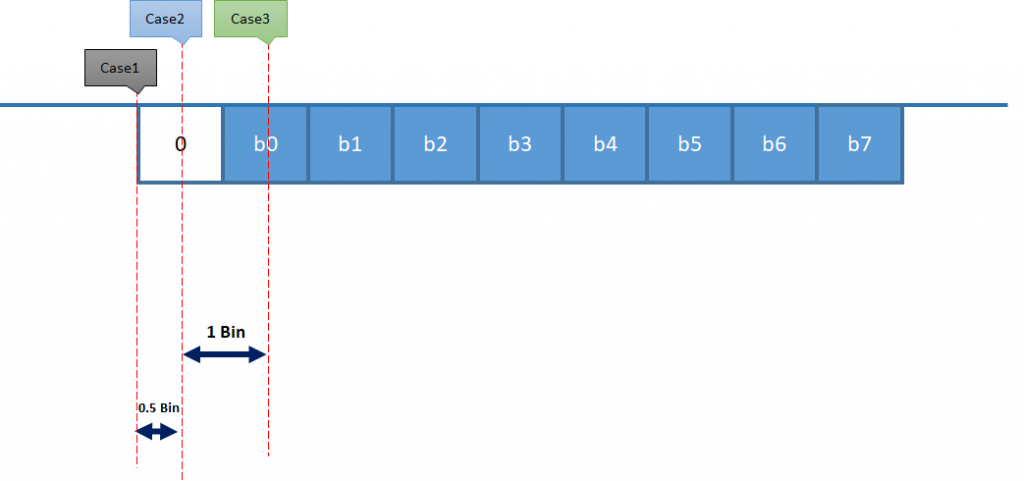

那第2狀態是甚麼呢?

其實有兩個方法

移動 0.5 bin 從 Start 到中間

移動 1.5 bin 直接進去 bin0

麻~ 最好的解當然是2,我就寫1,2留給你們自己練習

收一個 0.5 Bin的長度,如果超過 Bin 長度就跳到 State 3

一半為 288/2 =144

從0開始數所以減1 = 143

2:

begin

if(Count_clk >= 143 ) begin

Count_clk<=0;

State1 <= 3;

end

else begin

Count_clk<=Count_clk+1;

end

end

然後再將 State 3 也一樣移動 1 bin 到數據中間

2:

begin

if(Count_clk >= 143 ) begin

Count_clk<=0;

State1 <= 3;

end

else begin

Count_clk<=Count_clk+1;

end

end

3:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

State1 <= 4;

end

else begin

Count_clk<=Count_clk+1;

end

end

將這段加入程式碼

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

reg[7:0] State1;

reg[7:0] Count_clk;

reg[7:0] Count_bin;

reg[7:0] Data_Previous1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Count_clk<=0;

Count_bin<=0;

Data_Previous1<=0ㄤ

State1 <=0;

end

else begin

Data_Previous1 <= Data1;

case (State1)

0:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

end

else begin

Count_clk <= Count_clk + 1;

end

if(Count_clk == 0 )begin

if(Data1==1)begin

Count_bin <= Count_bin+1;

end

else begin

Count_bin <= 0;

end

end

if(Count_bin== 15 )begin

State1 <= 1;

end

end

1:

begin

if(~Data_Previous1 & Data1 ) begin

State1 <= 2;

end

end

// 將這段加入程式碼

2:

begin

if(Count_clk >= 143 ) begin

Count_clk<=0;

State1 <= 3;

end

else begin

Count_clk<=Count_clk+1;

end

end

3:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

State1 <= 4;

end

else begin

Count_clk<=Count_clk+1;

end

end

default:

begin

end

endcase

end

end

endmodule

進入 b0 要做甚麼呢 紀錄數據阿,紀錄再 Output的 第0位

所以 Out1 是個 reg

reg[7:0] Out1;

設定為 Reg 就要馬上給他初始化

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

reg[7:0] State1;

reg[7:0] Count_clk;

reg[7:0] Count_bin;

// 所以 Out1 是個 reg

reg[7:0] Out1;

reg[7:0] Data_Previous1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

//設定為 Reg 就要馬上給他初始化

Out1<=0;

Count_clk<=0;

Count_bin<=0;

Data_Previous1<=0ㄤ

State1 <=0;

end

else begin

Data_Previous1 <= Data1;

case (State1)

0:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

end

else begin

Count_clk <= Count_clk + 1;

end

if(Count_clk == 0 )begin

if(Data1==1)begin

Count_bin <= Count_bin+1;

end

else begin

Count_bin <= 0;

end

end

if(Count_bin== 15 )begin

State1 <= 1;

end

end

1:

begin

if(~Data_Previous1 & Data1 ) begin

State1 <= 2;

end

end

// 將這段加入程式碼

2:

begin

if(Count_clk >= 143 ) begin

Count_clk<=0;

State1 <= 3;

end

else begin

Count_clk<=Count_clk+1;

end

end

3:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

State1 <= 4;

end

else begin

Count_clk<=Count_clk+1;

end

end

default:

begin

end

endcase

end

end

endmodule

最後將 讀到的 Data 付值到 Out1的第0位

3:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

// 讀到的 Data 付值到 Out1的第0位

Out1[0] <=Data;

State1 <= 4;

end

else begin

Count_clk<=Count_clk+1;

end

end

加到程式碼吧

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

reg[7:0] State1;

reg[7:0] Count_clk;

reg[7:0] Count_bin;

// 所以 Out1 是個 reg

reg[7:0] Out1;

reg[7:0] Data_Previous1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

//設定為 Reg 就要馬上給他初始化

Out1<=0;

Count_clk<=0;

Count_bin<=0;

Data_Previous1<=0ㄤ

State1 <=0;

end

else begin

Data_Previous1 <= Data1;

case (State1)

0:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

end

else begin

Count_clk <= Count_clk + 1;

end

if(Count_clk == 0 )begin

if(Data1==1)begin

Count_bin <= Count_bin+1;

end

else begin

Count_bin <= 0;

end

end

if(Count_bin== 15 )begin

State1 <= 1;

end

end

1:

begin

if(~Data_Previous1 & Data1 ) begin

State1 <= 2;

end

end

// 將這段加入程式碼

2:

begin

if(Count_clk >= 143 ) begin

Count_clk<=0;

State1 <= 3;

end

else begin

Count_clk<=Count_clk+1;

end

end

3:

begin

if(Count_clk >= 287 ) begin

Count_clk<=0;

// 讀到的 Data 付值到 Out1的第0位

Out1[0] <=Data;

State1 <= 4;

end

else begin

Count_clk<=Count_clk+1;

end

end

default:

begin

end

endcase

end

end

endmodule

那我們走到了