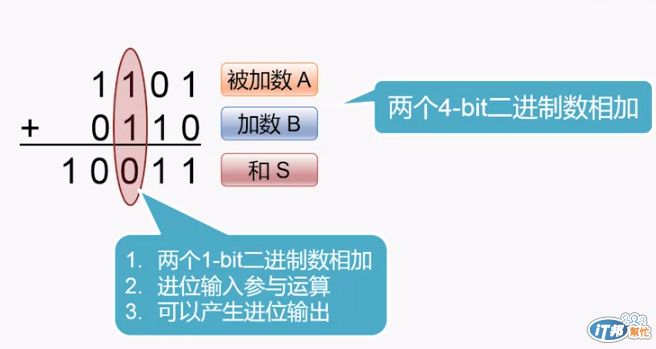

上圖是一個 4bits 的加法運算,我們可以看到在處理一個 bit 時會有三個步驟

分別是先將被加數和加數的 bit 值相加,之後再加上進位的值

最後產生該 bit 的和以及進位輸出

那這個加法運算在電路上是怎麼實現的呢

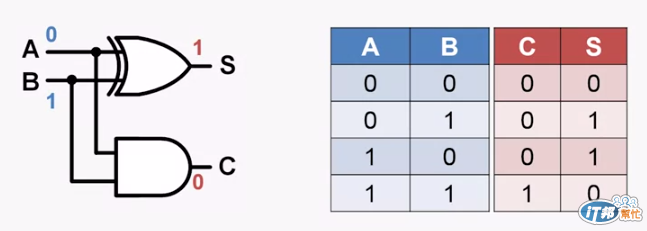

首先先來看半加器,右邊是加法運算的真值表

因此我們可以看到 Carry(進位) 可以用 AND 邏輯閘

Sum(總和) 則是使用 XOR 邏輯閘

但是他只能處理兩個來源,而沒有考慮到進位的輸入

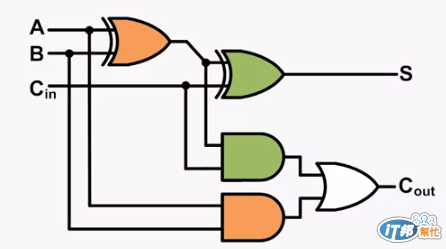

因此接下來就是由兩個半加器所構成的全加器:

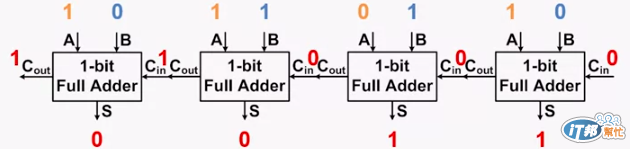

再把四個全加器如下圖串接起來,

前一個 Cout 是下一個的 Cin,而加數與被加數則分別連到 AB 端口

就可以成功計算本文最剛開始那個 4bits 的加法運算了

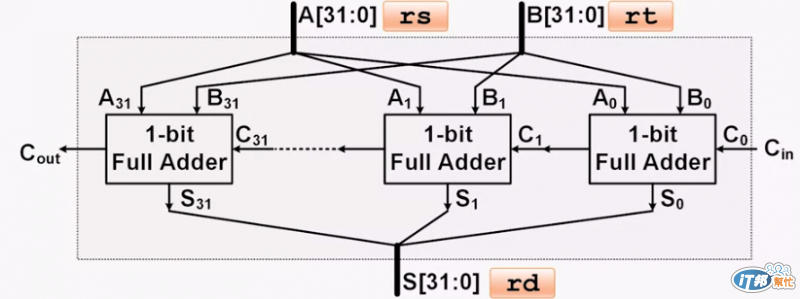

反應快的人可能就想到了:下圖就是在 ALU 中的 32bits 全加器

將 rs, rt 當作個別全加器的輸入,將結果輸出到 rd 中

關於 MIPS R型的加法指令有 add rd, rs, rt 和 addu rd, rs, rt 兩種

之前在 MIPS 體系結構中跳過沒細講,下一篇將會繼續介紹這兩種指令的差別