昨天我們的裝備已經有 and、nand、or、nor 和 xor、xnor

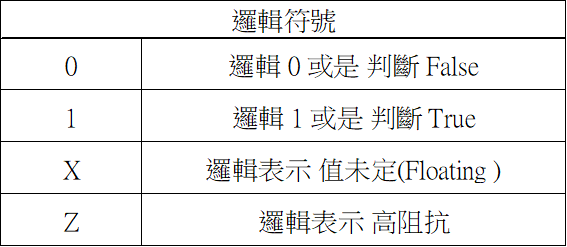

今天來一下 NOT(Inverter) 跟 Buf(YES)

老樣子 我們先假設:

輸入是 A ,我們今天要加入一個觀念,

有機會出現的結果不是 0 1 而是:

X 邏輯表示 值未定(Floating )

Z 邏輯表示 高阻抗

後面我們會用到 高阻抗

Buf NOT 在數位邏輯中,有可能為了實現緩衝或放大..等等 用的閘。

Buf跟 Not 剛好是相反的輸出

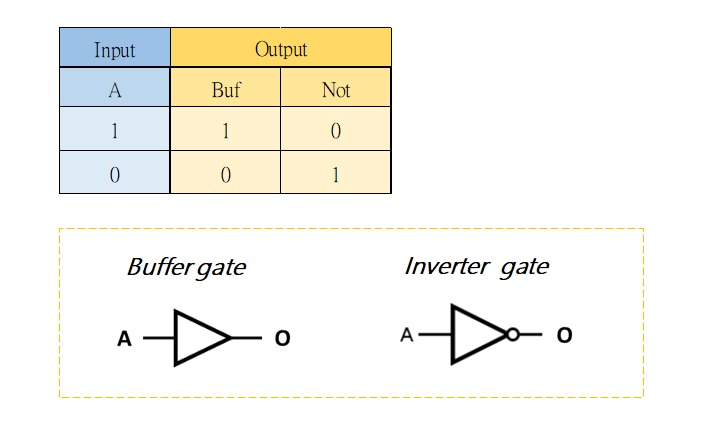

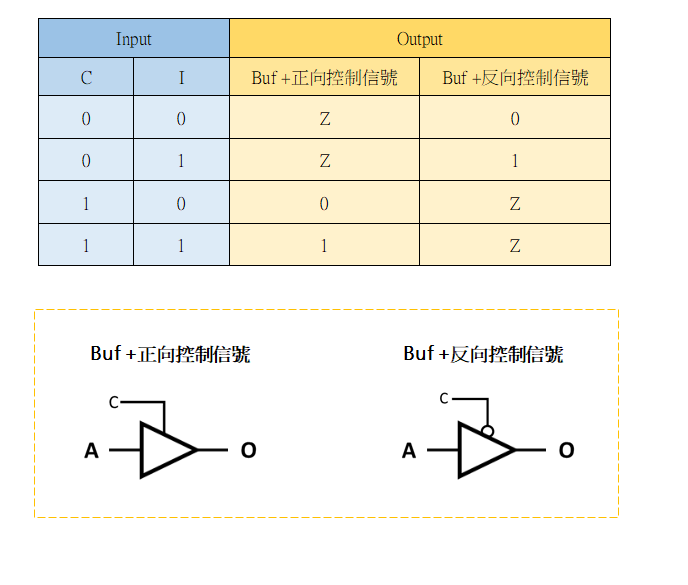

現在我們將 Buf 加入一個 控制信號 C,控制信號

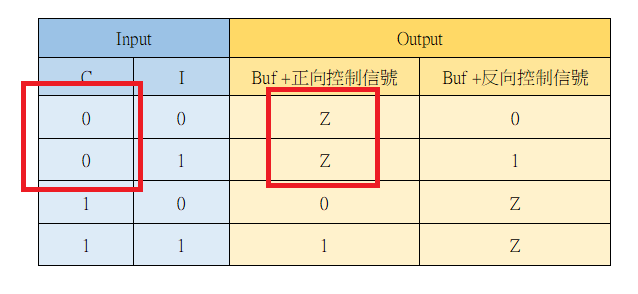

這其實相當簡單的想法,如果控制信號沒有打開 也是 C = 0 時,

輸出就只是個阻抗,所以:

其他同理

今天就到這吧~ 各位 掰掰

ヒトサンマルマル。そうねぇ、やっぱ昼はカレーだよねぇー!間宮カレー、行きますかねぇ?それとも、半舷上陸しちゃう?

其實我忘掉這段了要講不然應該是昨天講 哈哈

出個作業好了,Inverter 加入控制信號 C 會怎樣呢?