我們終於要踏上Vivado的海域了,一起裝載九三式氧推進魚雷出發吧

安裝 Verilog 我推薦一個寫的非常好的Sheng大大在2018年鐵人賽的文章,最近在重裝的時候也是看他的文章

https://ithelp.ithome.com.tw/articles/10191489

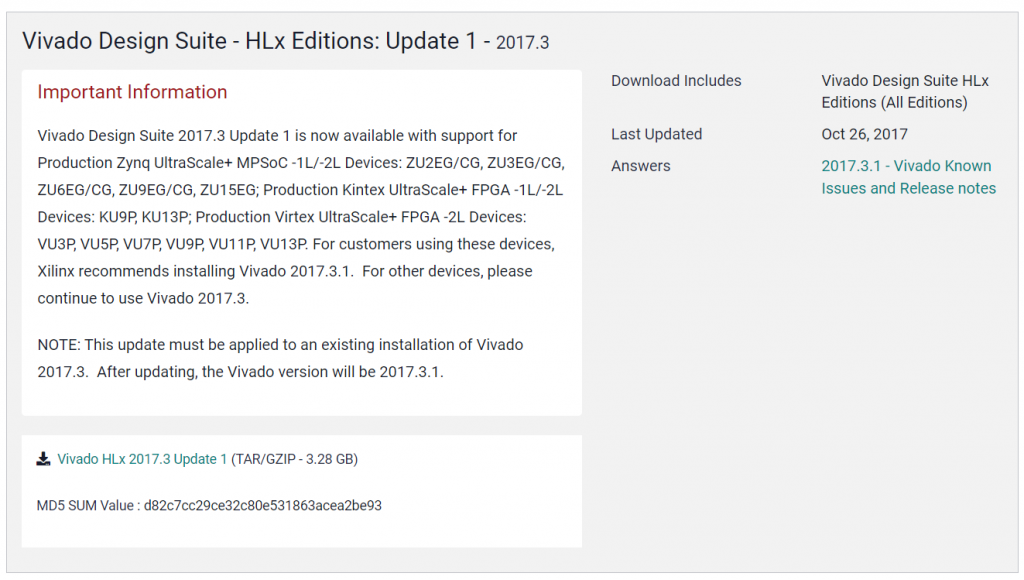

Xilinx 的 Vivado 下載網址在這裡,由於這只是入門教學,找一個能用的下載就好

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/archive.html

如果沒有帳號記得先去辦一個帳號

https://login.xilinx.com/app/xilinxinc_f5awsprod_1/exknv8ms950lm0Ldh0x7/sso/saml

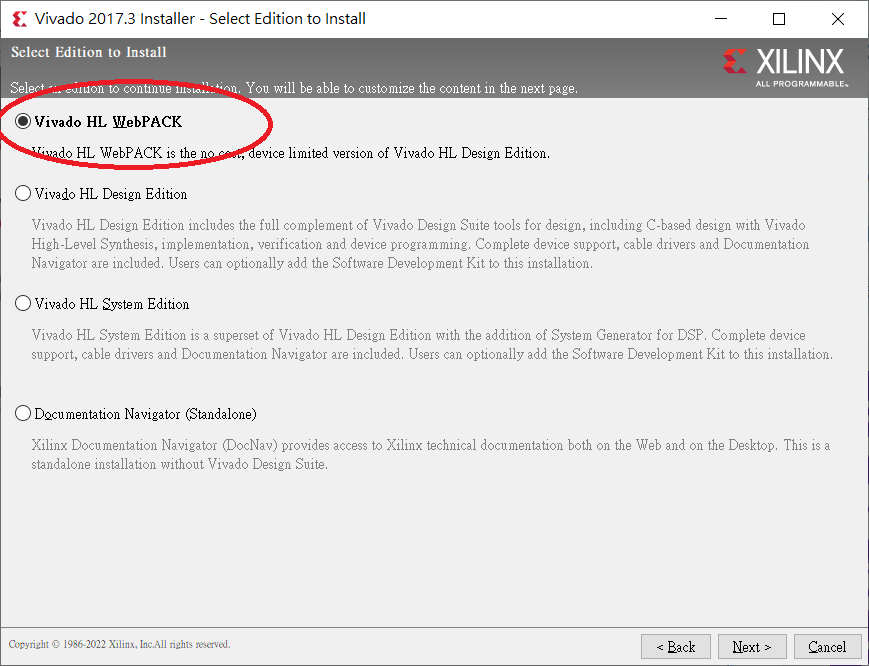

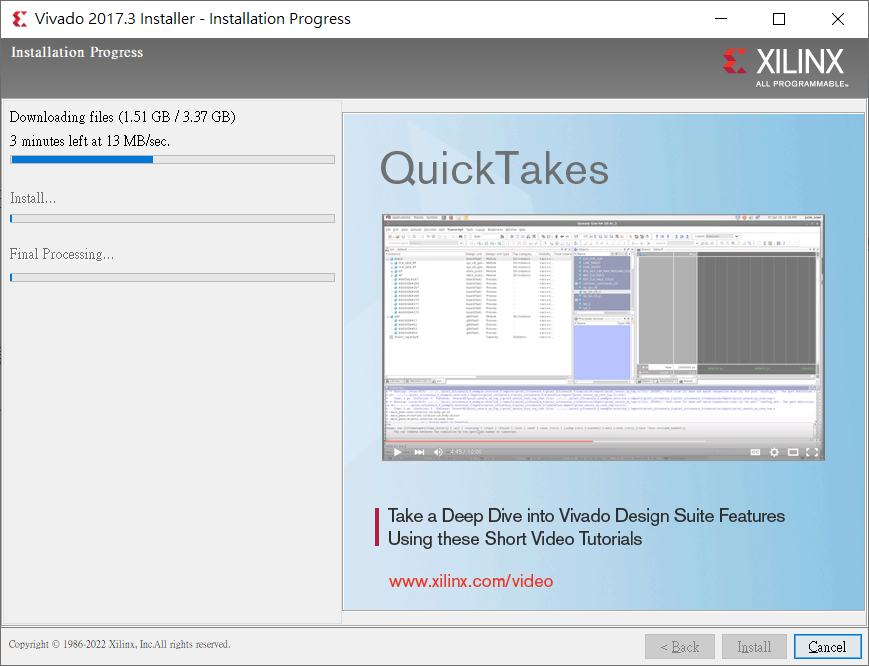

我目前是使用 Vivado 2017.3 來執行 安裝快 又比較小 新版的裝完就3小時了吧 哈哈

接下來就是一個漫長的安裝時間

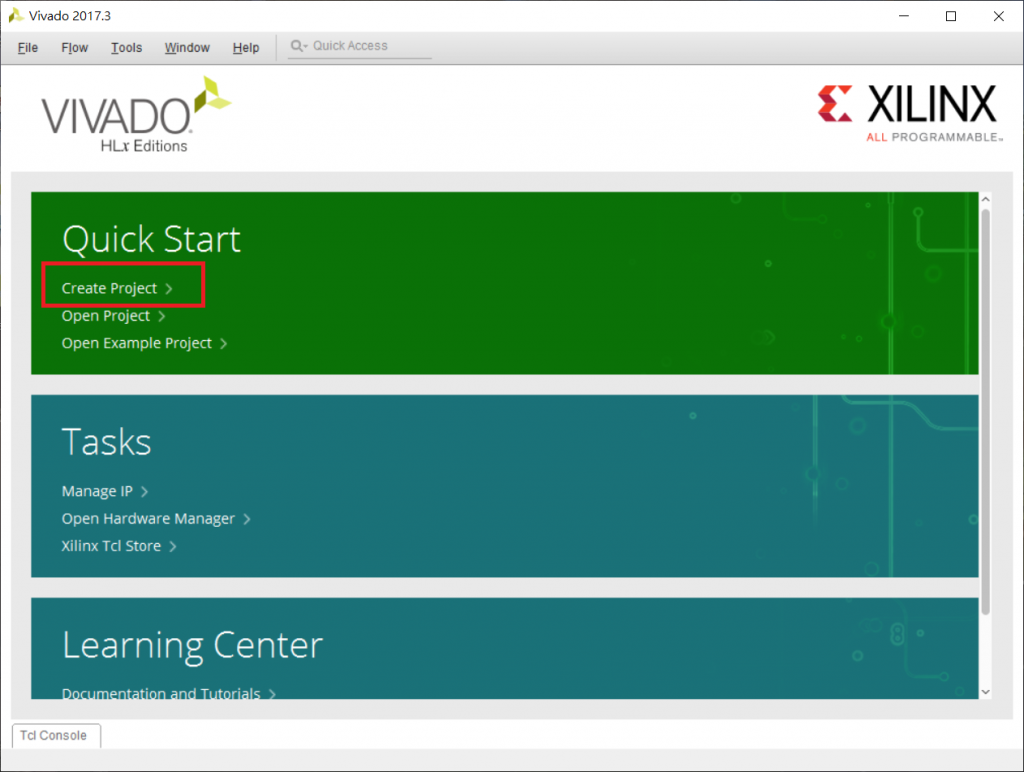

安裝完成之後點擊

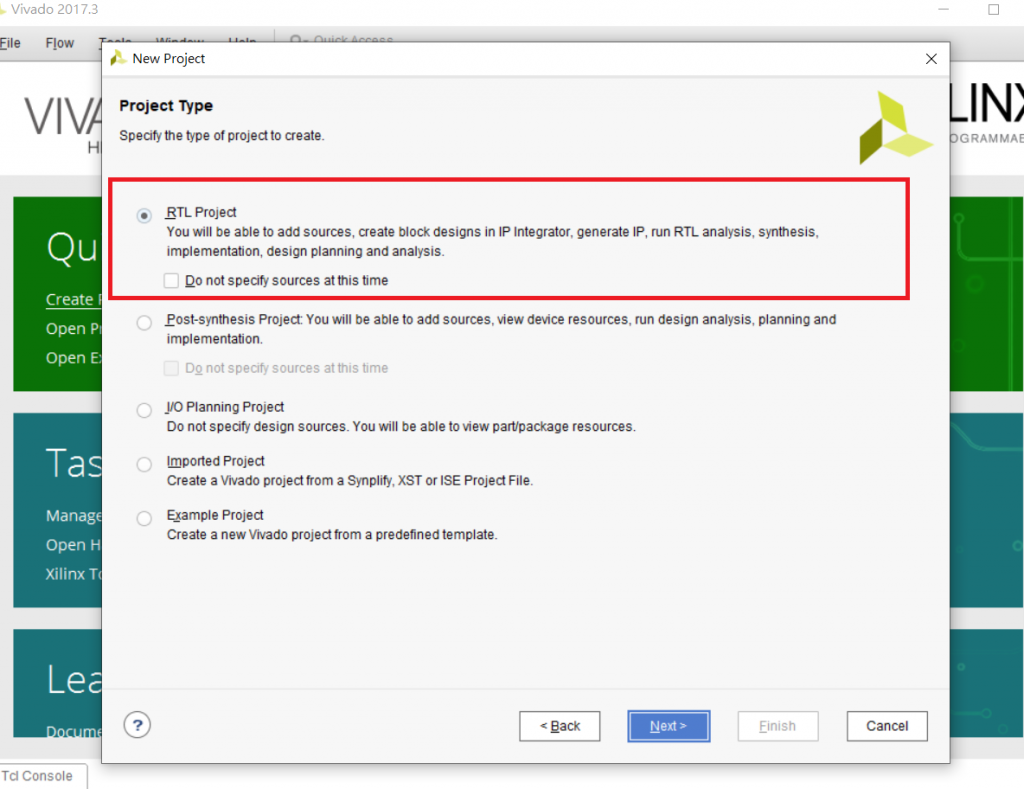

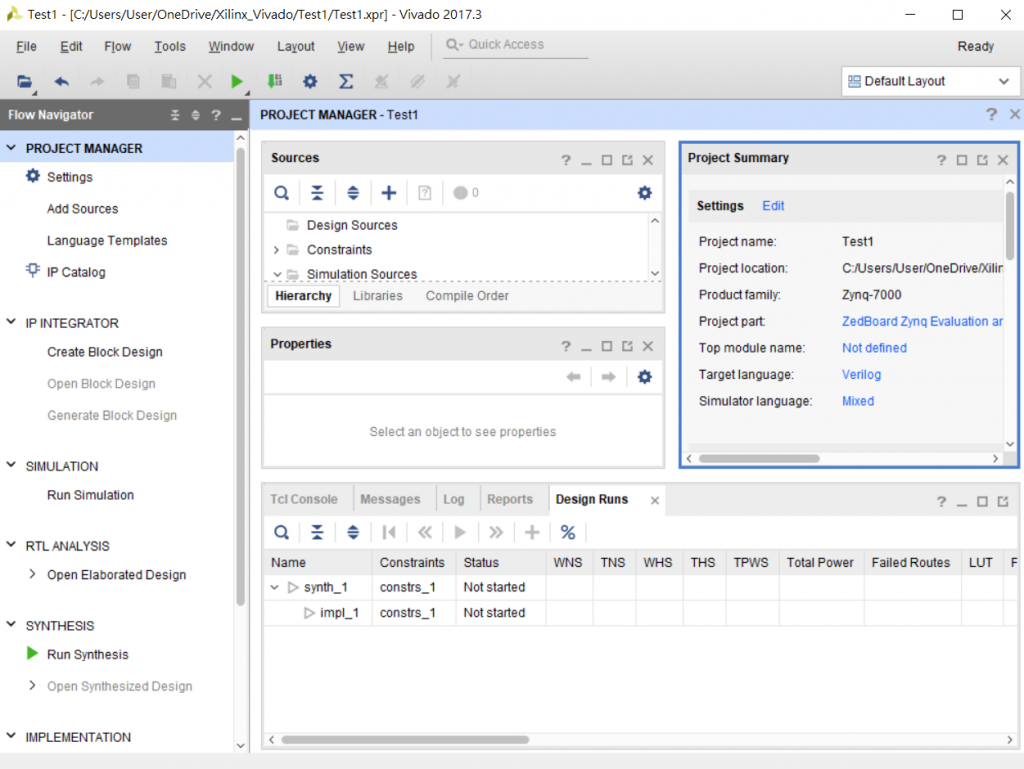

我們先創立一個專案吧

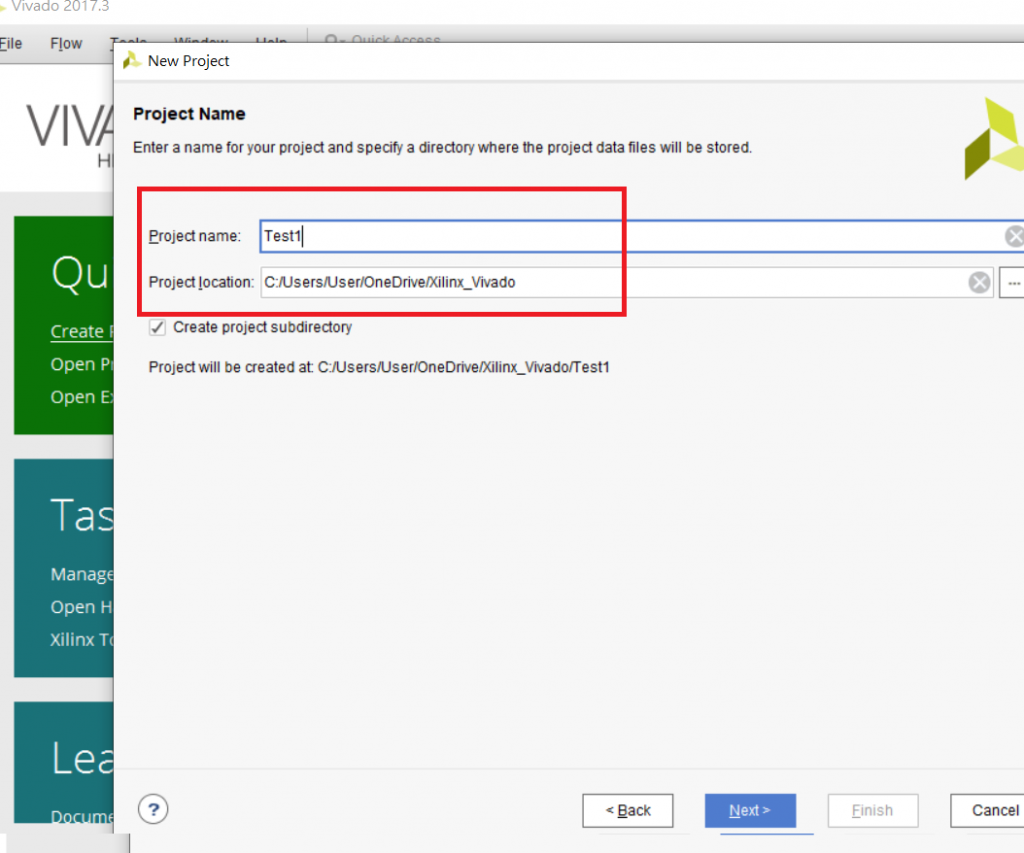

設定一個專案的名字

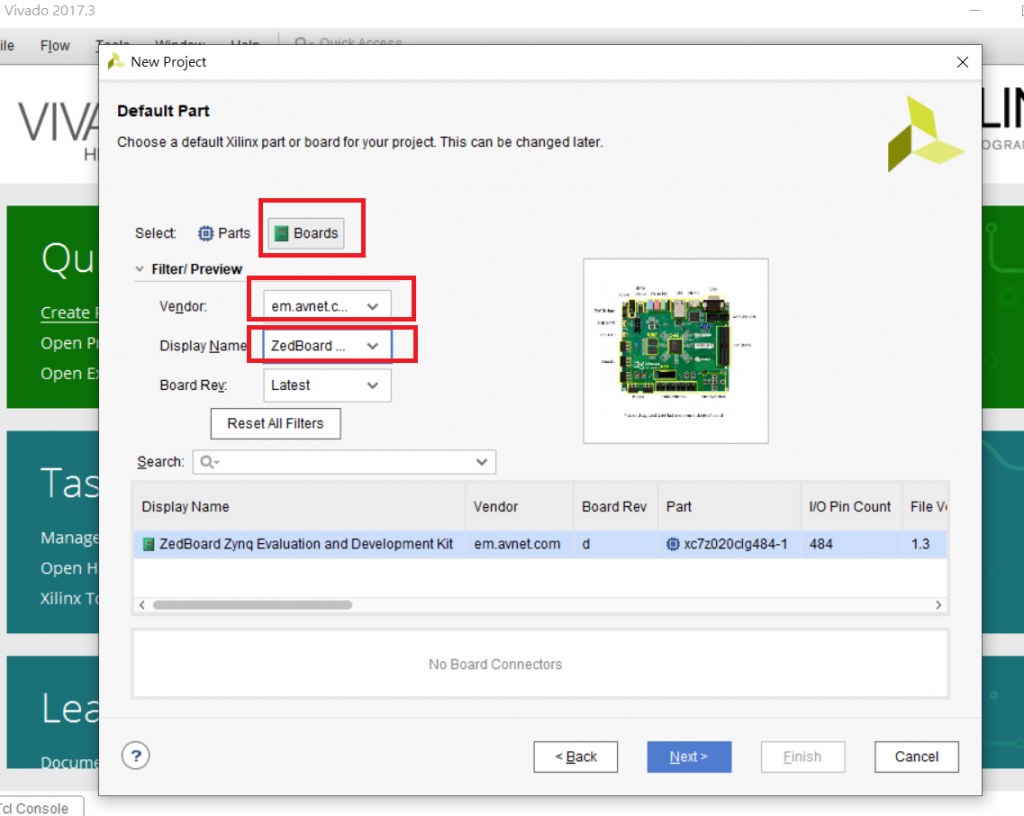

選好一個模擬的板子

** 以下只是快快跑一次程式看看 , 接下來才會認真講這在做什麼 **

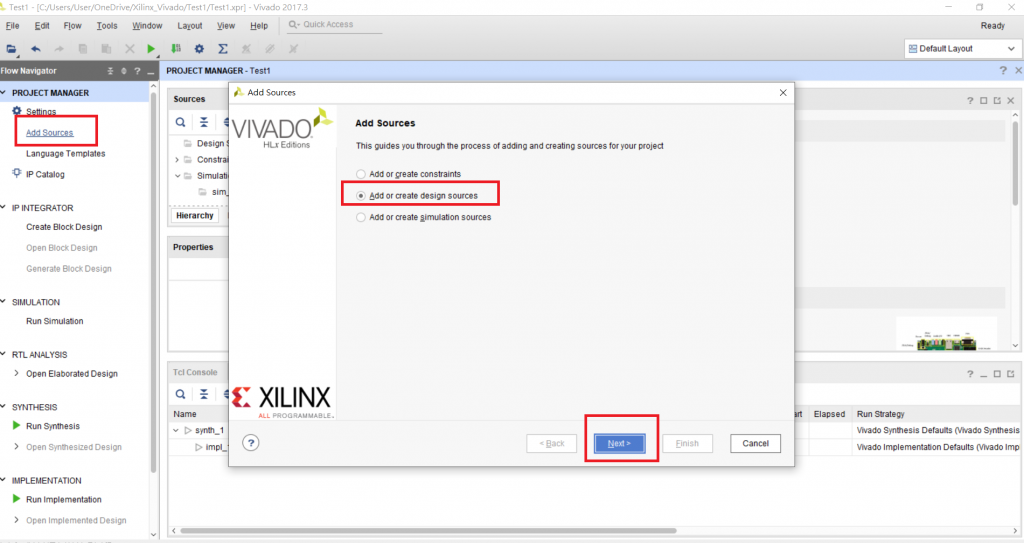

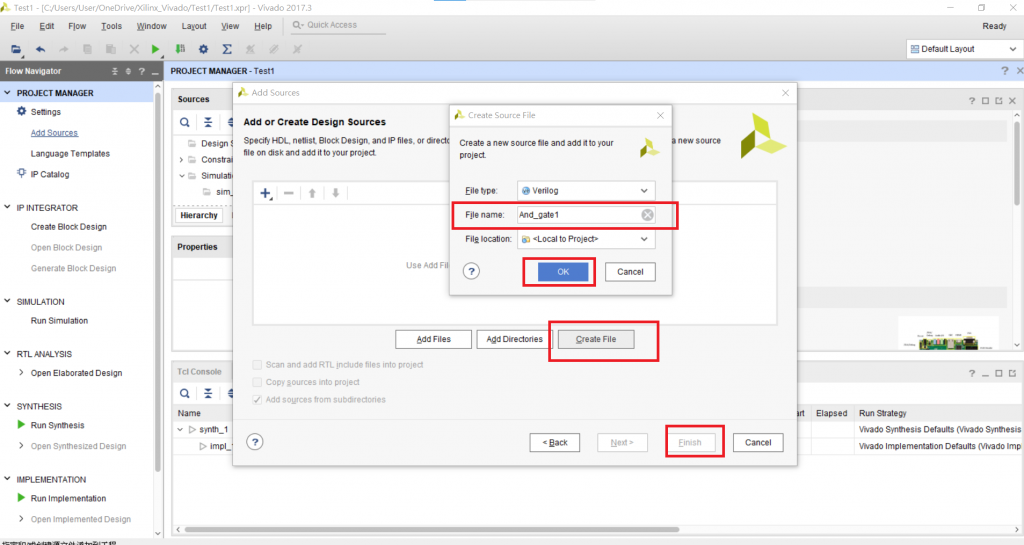

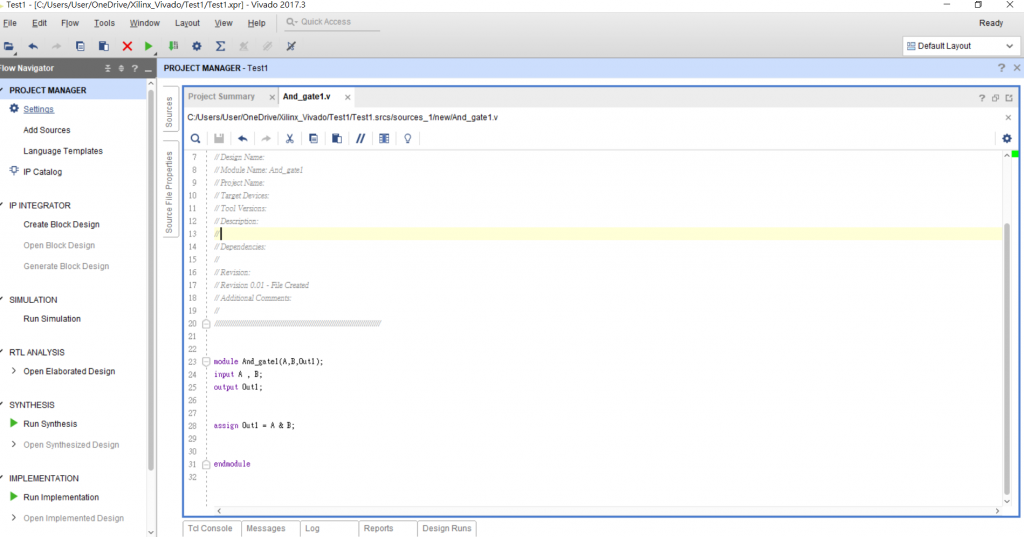

先建立一個文件 這次我們就式作 And Gate

打上這段程式碼

module And_gate1(A,B,Out1);

input A , B;

output Out1;

assign Out1 = A & B;

endmodule

輸入後 按存檔

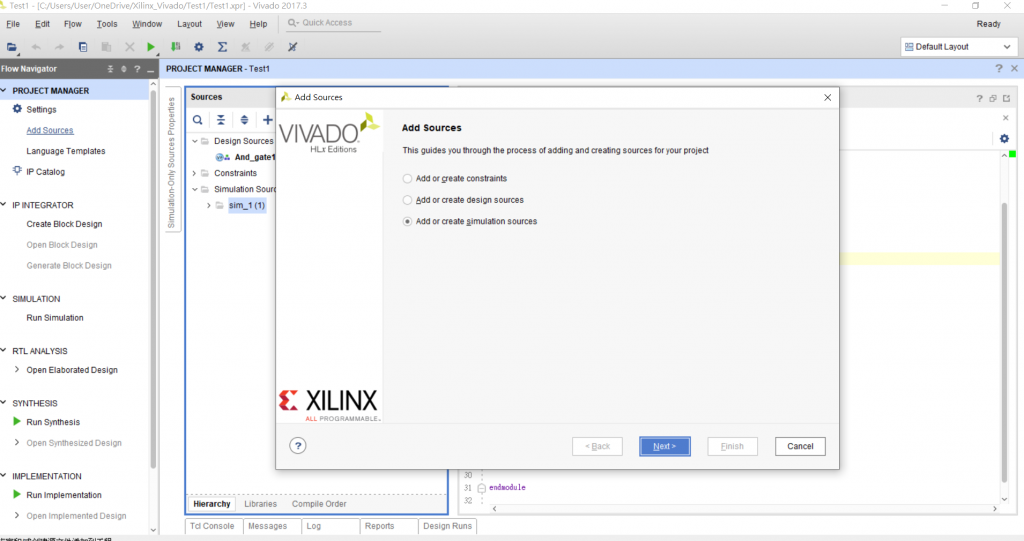

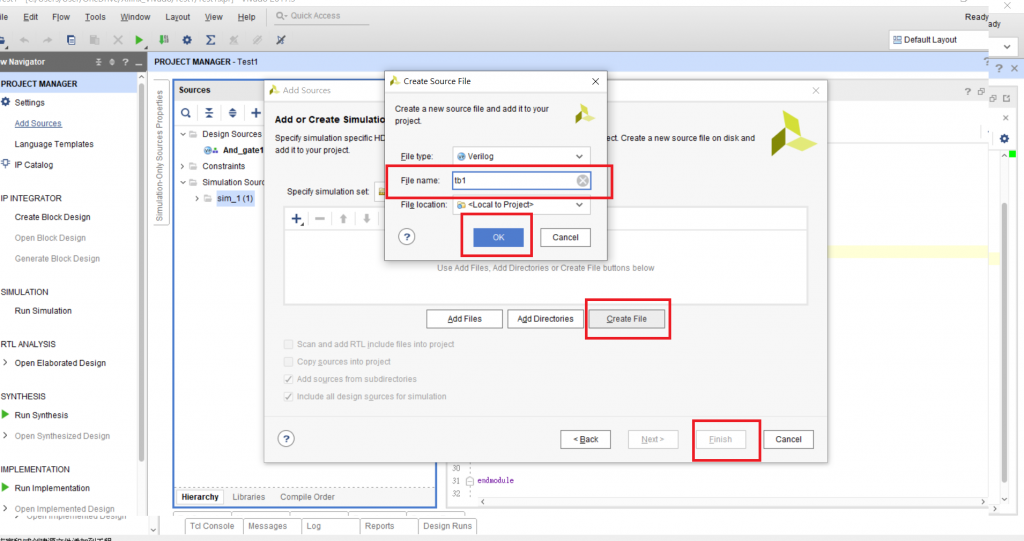

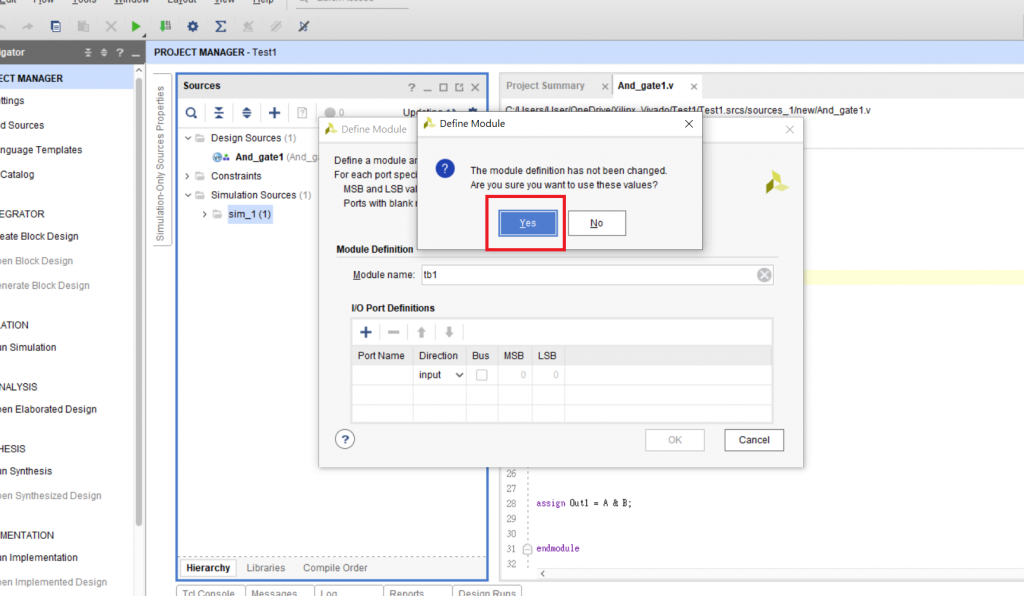

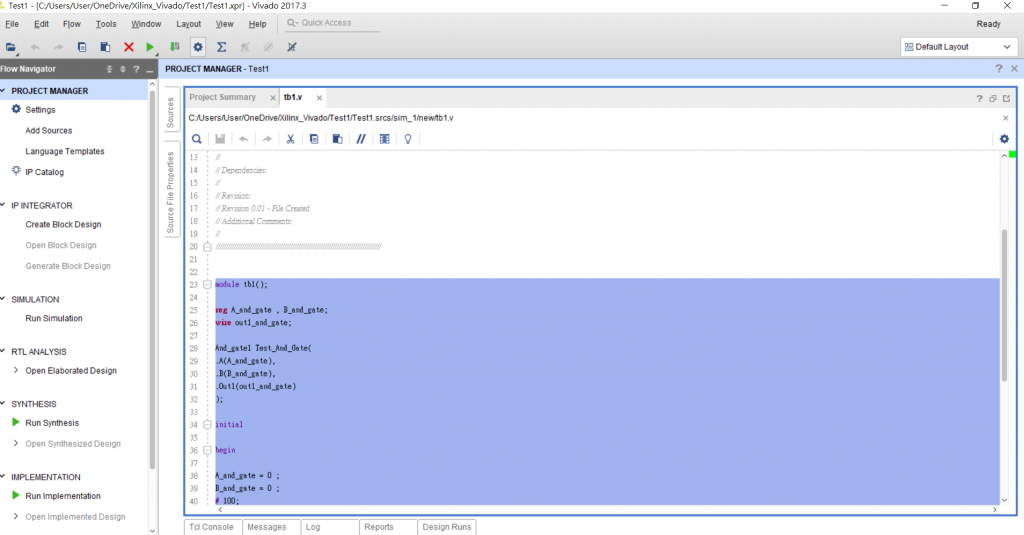

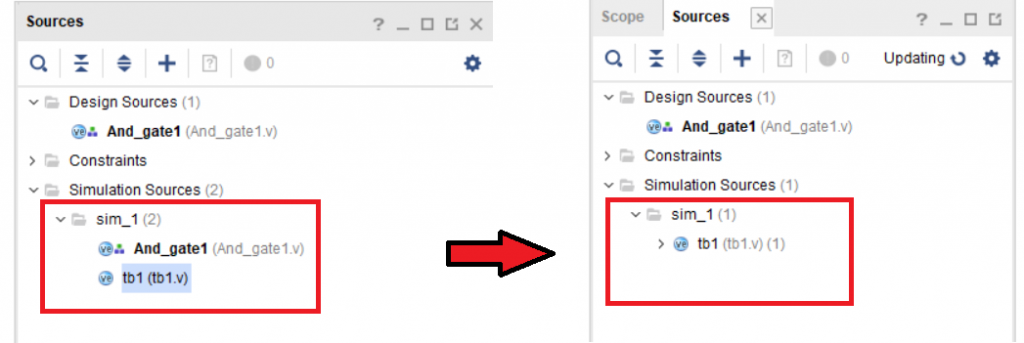

建立一個 測試程式 tb1

點開 tb1

寫下這段程式

module tb1();

reg A_and_gate , B_and_gate;

wire out1_and_gate;

And_gate1 Test_And_Gate(

.A(A_and_gate),

.B(B_and_gate),

.Out1(out1_and_gate)

);

initial

begin

A_and_gate = 0 ;

B_and_gate = 0 ;

# 100;

A_and_gate = 1 ;

B_and_gate = 0 ;

# 100;

A_and_gate = 0 ;

B_and_gate = 1 ;

# 100;

A_and_gate = 1 ;

B_and_gate = 1 ;

# 100;

end

endmodule

按下存檔

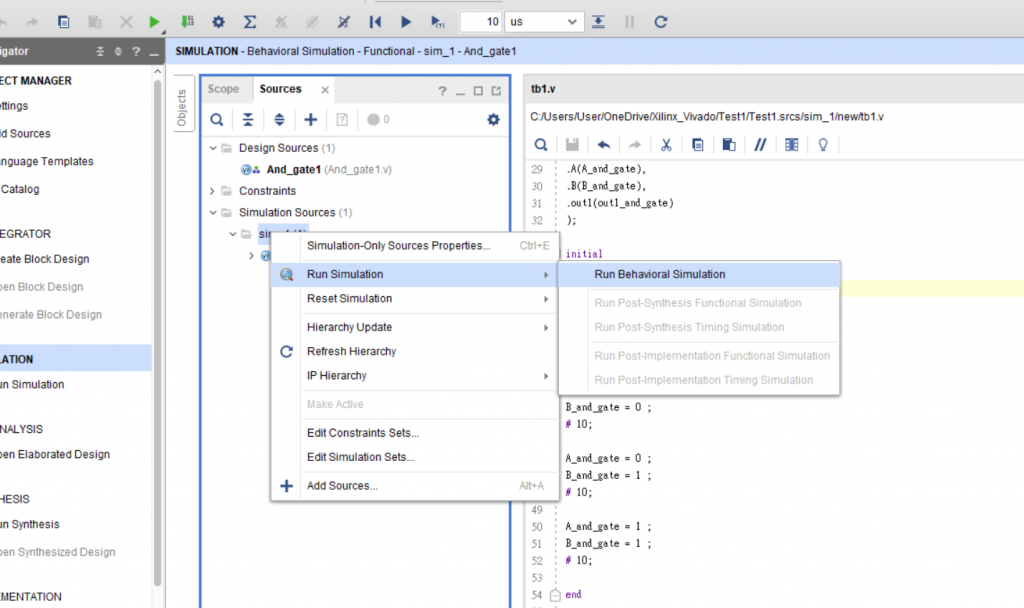

開始模擬

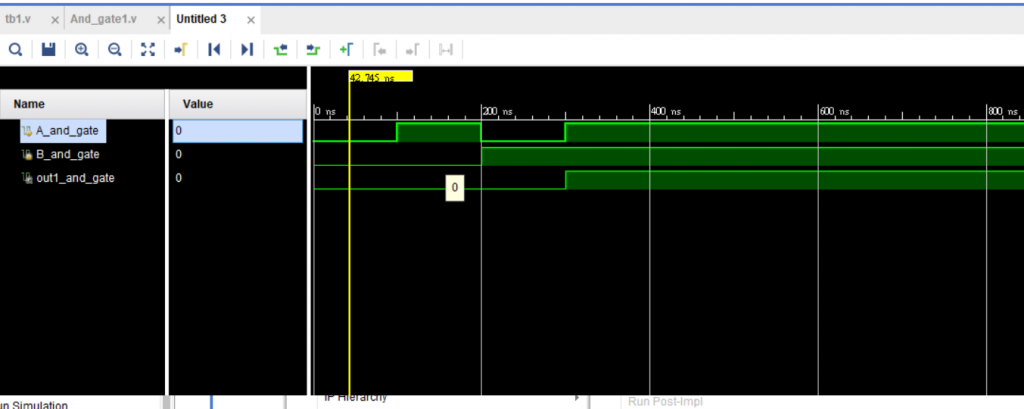

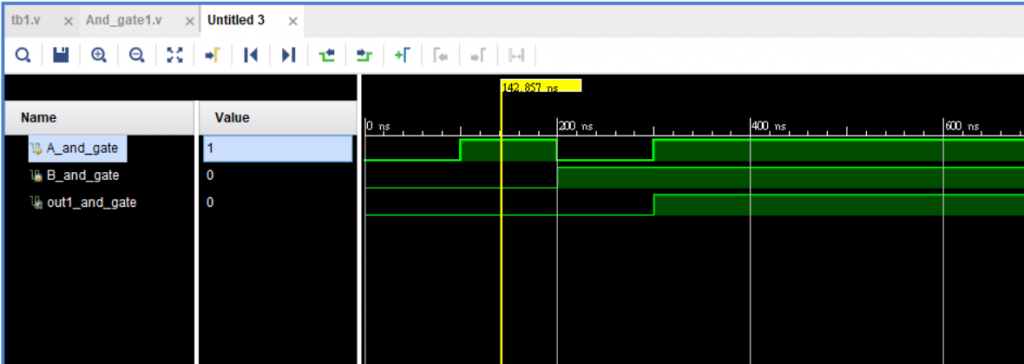

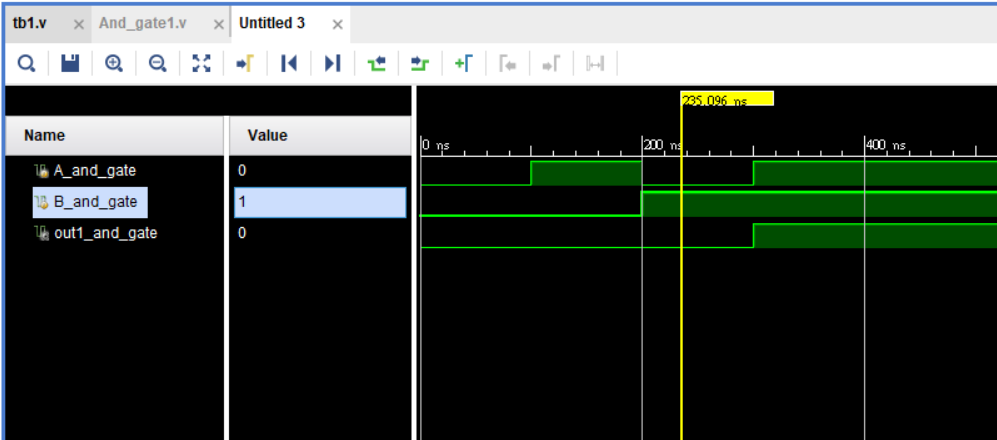

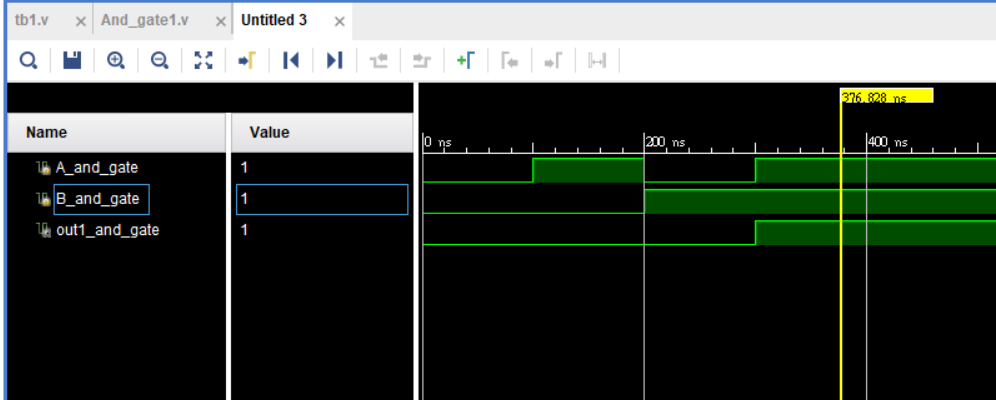

來看看結果

A = 0 、B = 0 → Out = 0

A = 0 、B = 1 → Out = 0

A = 1 、B = 0 → Out = 0

A = 1 、B = 1 → Out = 1

明天才要講解喔 現在粗看而已

好了 收工 剛好 12點來去吃飯~

ヒトフタマルマル。お昼だぁー。さて、今日は何食べに行こうかねぇ。うーん。