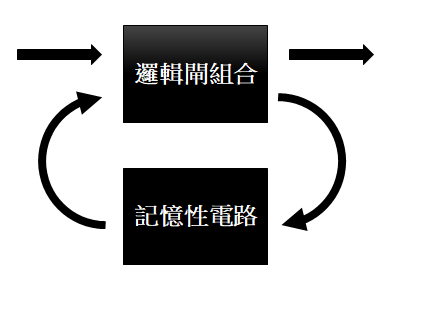

我記得一開始有講,我覺得 Verilog 是一個畫圖軟體

(PS 昨天說要畫圖,想一想推到後面再說)

今天沒有要開 Vivado 我們講講下幾天要做的事情

P2海域就是個入門的測計,入門設計大概是:

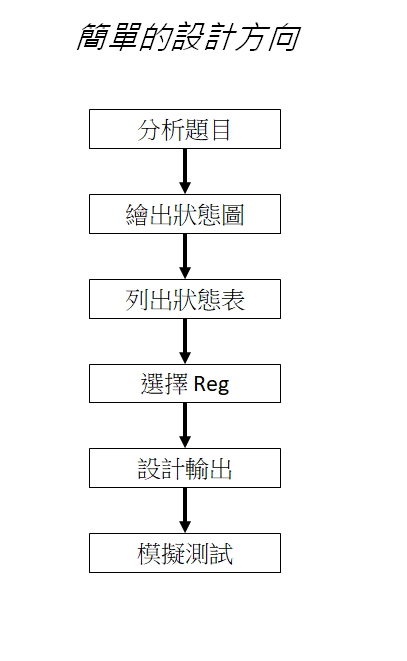

那簡單的想法方向就是:

現在只是快速講講,實際還是後面詳細慢慢講

分析題目

就是看到輸入的方式與輸出的方式,舉例

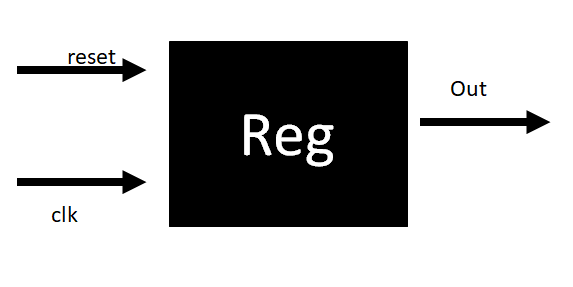

我們就舉一個昨天的簡化版要設計一個:

匯出圖形

這次很簡單 大概畫一下

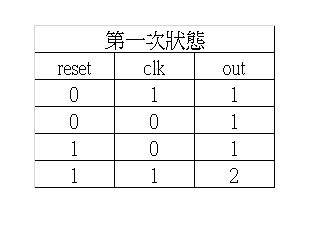

列出狀態表

大概寫一下

一開始狀態:

用畫圖的更好,但是懶得用電腦畫 就用表將就一下

選擇 Reg

這個Reg就是大概是哪一種Reg

大概就是 時序那邊的 Counts, 如果想知道 Psoc的東西 到時再補完

設計輸出

打開 vivado 來設計

(昨天的意思意思貼一下)

module Clk_Add3(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=1;

end

else begin

if(Out1==8) begin

end

else begin

Out1 <= Out1<<1;

end

end

end

endmodule

模擬測試

寫個 TB來測試看看

(昨天的意思意思貼一下)

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

Clk_Add3 Test1(.reset1(reset1),.clk(clk),.Out1(Out1));

initial begin

clk<=0;reset1<=0;

#7 reset1<=1;

#6000 $stop;

end

always #5 clk<=~clk;

endmodule

大概這樣今天加班有點晚,中午有再想要寫甚麼,所以水一集 真是抱歉了

フタフタマルマル。さっ、そろそろ本日の艦隊勤務もおしまいですよ~。ご苦労様でした~。寝よ寝よ。提督、それじゃ。