首先自己以「CPU」、「RISC」、「IEEE」作為關鍵字搜尋,並挑選出了下述三篇論文,並且提供每個對應的摘要截圖

由基本的摘要中我們可以看出第一個命題是對CPU架構的硬體安全問題進行探討,這方面是不同於課堂上架構與設計理念的介紹,也是自己第一次看到硬體安全性的相關資料之論文;第二個命題則是對於RISC的branch與cache的對比來比對處理器性能的評估與探討;而第三個命題則對RISC的演變由來、編碼、指令、邏輯、操作、硬體元件進行了詳細的介紹與分析,並且用Xilinx Virtex 6xc6vlx550t-2ff1759 型號的FPGA將其實現於AISC上(客製化IC)進行kernel測試與嘗試提出與修改出更好的硬體使用率策略。

而最後我選擇以第一篇論文作為本次的作業根據,雖然第三篇論文對於自己來說較好書寫、與上課學習的知識也有較高的契合度與可以做為ARM架構和RISC架構比較的好題材,但因為自己最近方認識硬體資安,也想趁本次機會對硬體的安全性維護進行更深的認識與學習,平常接觸的資安領域皆是以軟體為主,有幸找到本篇論文便產生了更深興趣想探究、研習。

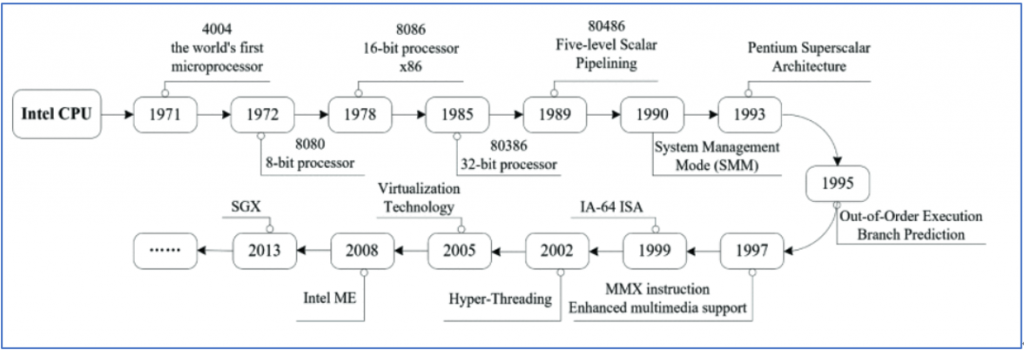

圖1.Intel CPU發展時程表

本圖表介紹了自1971年至2013年的CPU發展歷程,從CPU的起源、pipeline structure、1995年出現的out-of-order execution(亂序執行,可以達到高度平行化的實現)、branch prediction(分支預測,可以減少stall cycle時間)。由上述的進展我們可以觀察到CPU已逐漸邁向hyperthreading(超線程), virtualize, instruction set extension(指令集擴展)與達到remote management (遠程控制)等目標。

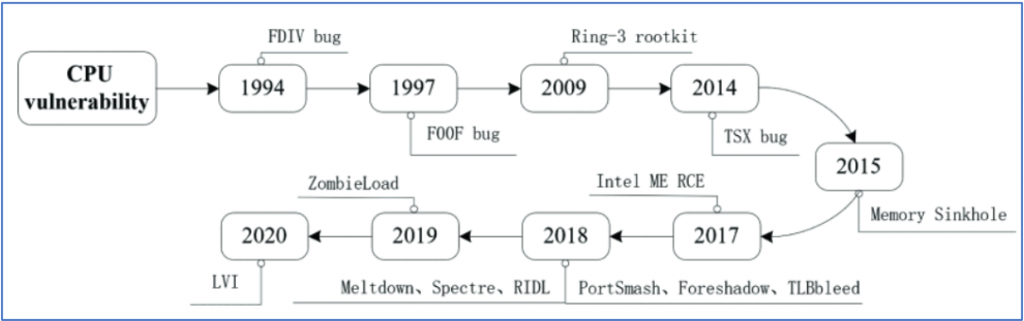

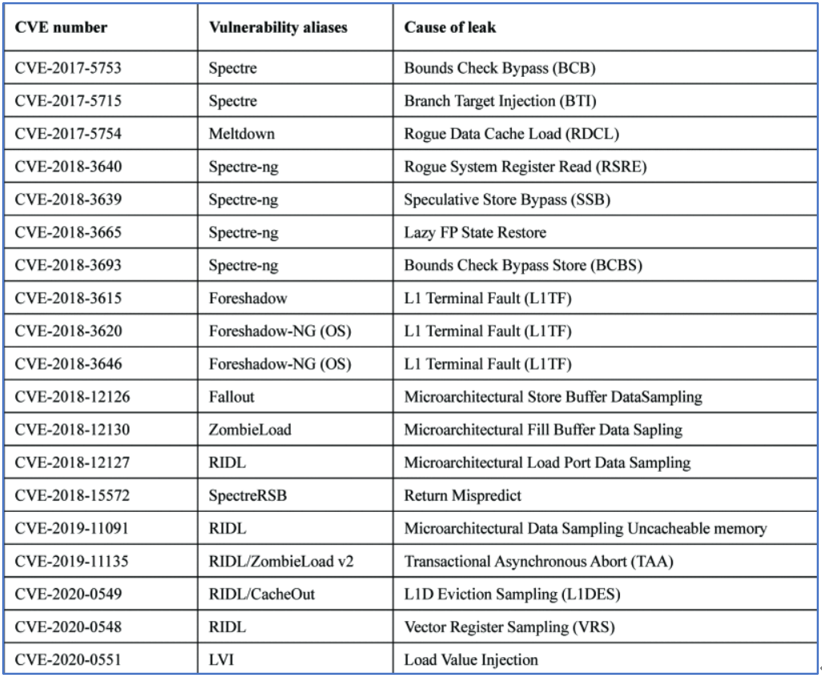

圖2. 主要CPU漏洞問題

而在這樣的發展下,本圖也提供了自CPU發展至今的安全問題。下述分別簡介之:

而本篇論文設立一假設:「instruction security(指令安全)是處理器安全的核心問題」。

而指令安全由下述三條件來達到CPU的安全:

而在本文中則會以「指令違規描述(instruction violation description)」、「執行優化技術(execution optimization technology)」、「劫持指令更新機制(hijacking instruction updating mechanism)」、「未記錄指令和後門(undocumented instruction and backdoor)」四項安全問題來探討,並以補丁修復(patch repair measures)和硬體保會技術(hardware protection technology)作為總結。

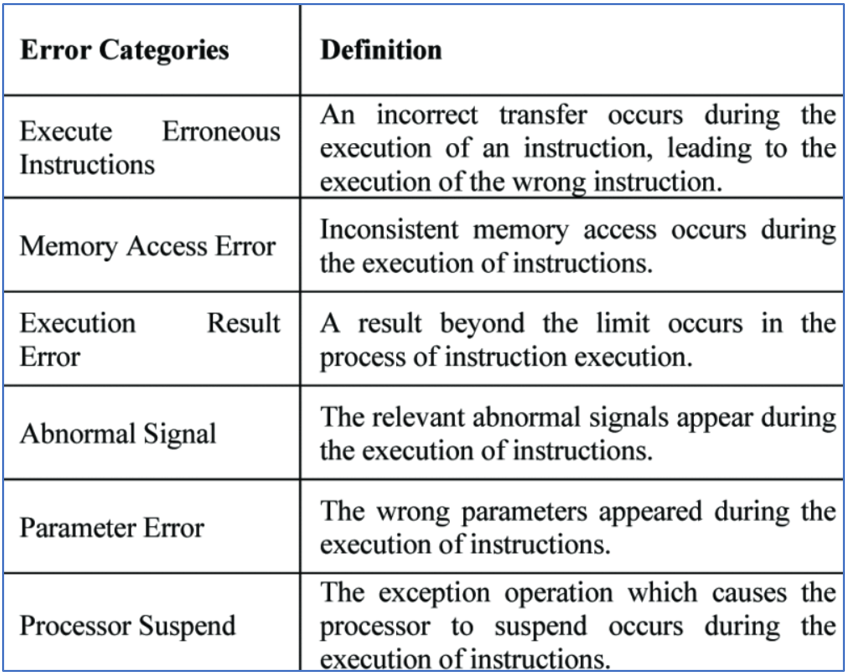

代表指令在CPU在違反ISA標準時program會產生的問題。此類的問題可以由CPU廠商所提供的勘誤表而得,我們根據CPU的工作機制可以將分為以下六種:

圖3. CPU implementation problem classification table

而由前述提供的漏洞問題,FDIV和FOOF的問題就屬於本類錯誤,也可以由此兩種範例再度證明違反ISA設計會對指令安全造成嚴重的影響。

由Introduction中我們提及CPU所使用的兩項技術,out-of-order execution(亂序執行)與branch prediction(分支預測)。

圖4. 指令執行機制導致的漏洞

舉例而言Meltdown bug便屬於此種問題。而多數的針對CPU的側道問題都是基於此兩種機制,也就是「優化技術的使用」而來。

在介紹劫持指令更新機制前,我們要先對微碼指令(Micro command),這是一種在CPU一周期內實現一定操作功能的一組微指令組合。通常這種指令會用來檢查控制指令的control unit,而一組指令也是由若干條的微碼所組成。而這樣的機制,卻也可能在更新時產生建構木馬(Trojan)的可能性。而這種由木馬而生的惡意負載而產生的問題就稱為劫持(hijacking),駭客可以由微碼鉤子(microcode hook)來達到遠程控制。我們可以透過供應商發出的勘誤表以補丁的方式來解決,或是利用更新加密機制(encrypted to check)的方式來避免。

因為現有的指令研究均需參考廠商發表的指令集定義,且相關的安全測試也需要由「具有源代碼(having source code)」作為前提。而這也導致若非CPU廠商很難對其進行安全測試。

因此,當時發展了Sandsifter,結合模糊測試與CPU指令測試來對於未紀錄的指令進行逆向分析(pure reverse analysis)使其成為指令分析(instruction set testing)。而後續又產生了CPU security benchmark,比Sandsifter更能跑在如arm或其餘的架構。

而在Sandsifter的研究上雖以演算法提升了搜索效率與準確性,但也發現目前大部分的處理器中包含了大量的未記錄指令,而因為這些指令的執行結果是未知的,其中也包含了在2018年的BlackHat中提到的VIA C3 processor中的後門問題(backdoor problem),使一般的用戶可透過此指令自行升級為超級用戶權限( super user privileges )。

而在2008年的另一項研究也以在ARM架構中添加流氓模式(rogue mode)使其可以任意使用rootkits 來隱藏不受OS security policies 所限制的指令。同樣在2009年也發現一個可以利用qemu virtual machine內置CPU後門的驗證方式。兩種案例都說明了backdoor problem所產生的極大危害。且因為這種內置後門(built-in backdoors)其實很難被開發者所發現,因此對於未記錄指令的研究也是很重要的一環。

前述在解決各類漏洞問題時我們常會以廠商定期發布的勘誤表和補丁(Patch)作為解法。

通常我們可以利用微碼補丁(microcode patch)的方式解決許多漏洞處理,其中以實現間接分支限制推測(Indirect Branch Restricted Speculation ,IBRS)、單線程間接分支預測器(Single Thread Indirect Branch Predictors ,STIBP)和間接分支預測器屏障(Indirect Branch Predictor Barrier ,IBPB)。而我們也會再加上如RSA等加密措施來防止前面提及的側道攻擊行為。但這些還不足以防止漏洞被利用的行為。

而微碼補丁也會有因需要等到漏洞出現才可校正與因加入了檢查措施導致的效能降低等缺陷。

硬體方面的保護包含了像是緩存分配技術指令集擴展(cache allocation technology ,CAT),可以透過支持軟體控制數據分析來分配last-level cache來隔離critical applications 與限制緩存。

而同時也可以藉由結合其他的硬體保護,像是Intel TSX便是希望能達成程序實現細粒度的鎖定性能,幫助檢測惡意行為並恢復與防止雲端服務的側道攻擊行為。

目前對於虛擬化技術與可信度平台(trusted computing technology)模塊的計算等系統安全的保護也得到了廣泛應用,但其中仍有許多不足,如虛擬化技術使用特權軟體(privileged software)來進行資源分配,而這也有可能導致潛在漏洞會破壞整個系統的隱憂。而對應措施也包含Intel推出安全指令集擴展(Software Guard Extensions ,SGX) 來以特殊的內存訪問控制技術,以保護應用程序被更高權限的訪問行為。

像前述提到的微碼木馬、VIA C3 processor God mode的後門問題以及無證指令(undocumented instruction)異常都會是未來的CPU安全重點。

對於各家廠商所公開的文檔時常會出現語意不同與真實行為與使用手冊不一致的行為,而因為很多的漏洞都需要藉由官方文檔來進行安全測試,那麼這些不一致的問題就會時常產生不符預期的延宕與死機狀態。若我們有更全面的語意分析與勘誤的研究也會視後續的研究重點。

在許多非CPU廠商的安全研究者的關注下,指令分析時常無法與逆向分析離開關係(像是前面提到的Sandsifter),也因為廠商不會公開完整的CPU內部結構與設計,因且這方面也會是未來研究的重要面向。

在本次的要求下,因緣際會自己得到了對於硬體資安的研究素材,從前看到的資安教材總是以軟體、網路層面講述問題,較少出現詳細介紹硬體層面資安維護的資料。加上上週末自己在iThome鐵人賽的頒獎典禮上與影片組冠軍的得主聊了許多資安資料,恰好在當時第一次接觸了「硬體資安」這個名詞,因為從前總認為資安都需要數學能力超群的人才可以接觸,而經過那次的談論也才開闊了自己的視野,因緣際會下,在搜尋資料時便被此篇論文吸引了目光。而在進行論文的分析與背景知識的搜索下,也認識了許多原本不曾想過的問題與知識,尤其是在introduction與conclusion中的兩句話也十分吸引自己的目光:” The booming development of CPU also brought many security problems”, ”characteristics are vulnerabilities.” 有別於上課專注於效能提升或架構介紹的角度,首次,自己跟著作者的闡述由安全層面來思考這些在科技發展下所產生的相對問題與其解法,也格外地收穫良多!