一般來說 tb 就是要測試這個function對不對

這篇文章就是要測試一下昨天寫的 module And_gate1(A,B,Out1);

昨天寫了一個

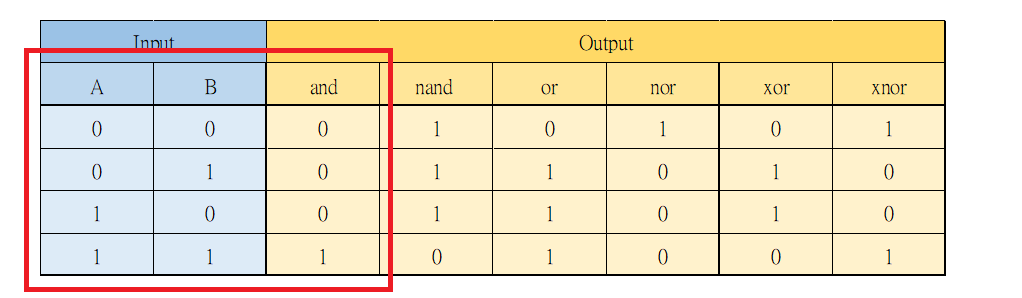

所以就是來執行看看 and gate

很簡單我們就試試看

回到第4天的

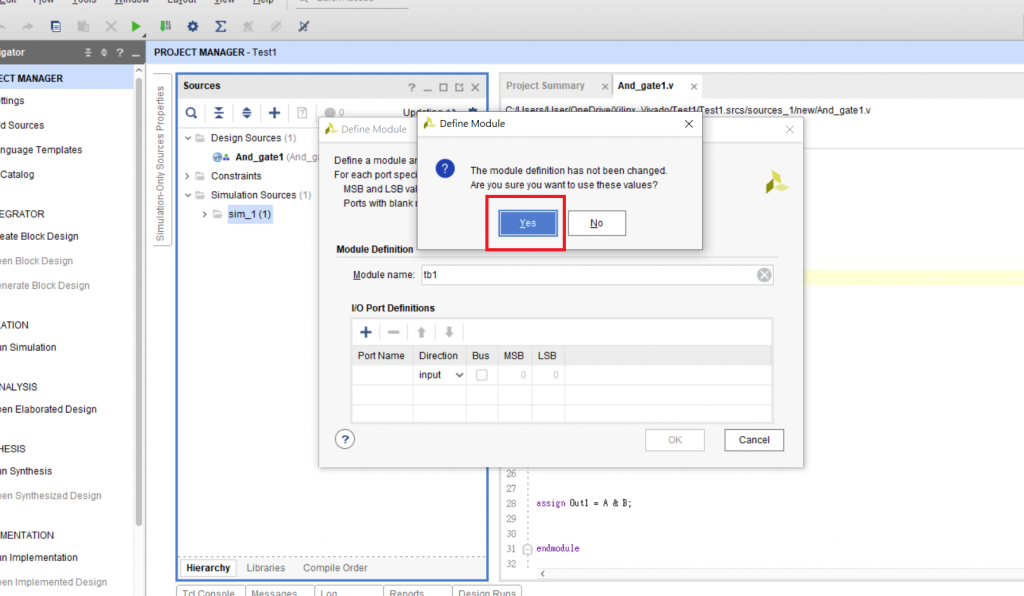

開起來大概長這樣

接下來將程式碼寫進去

module tb1();

reg A_and_gate , B_and_gate;

wire out1_and_gate;

And_gate1 Test_And_Gate(

.A(A_and_gate),

.B(B_and_gate),

.Out1(out1_and_gate)

);

initial

begin

A_and_gate = 0 ;

B_and_gate = 0 ;

# 100;

A_and_gate = 1 ;

B_and_gate = 0 ;

# 100;

A_and_gate = 0 ;

B_and_gate = 1 ;

# 100;

A_and_gate = 1 ;

B_and_gate = 1 ;

# 100;

end

endmodule

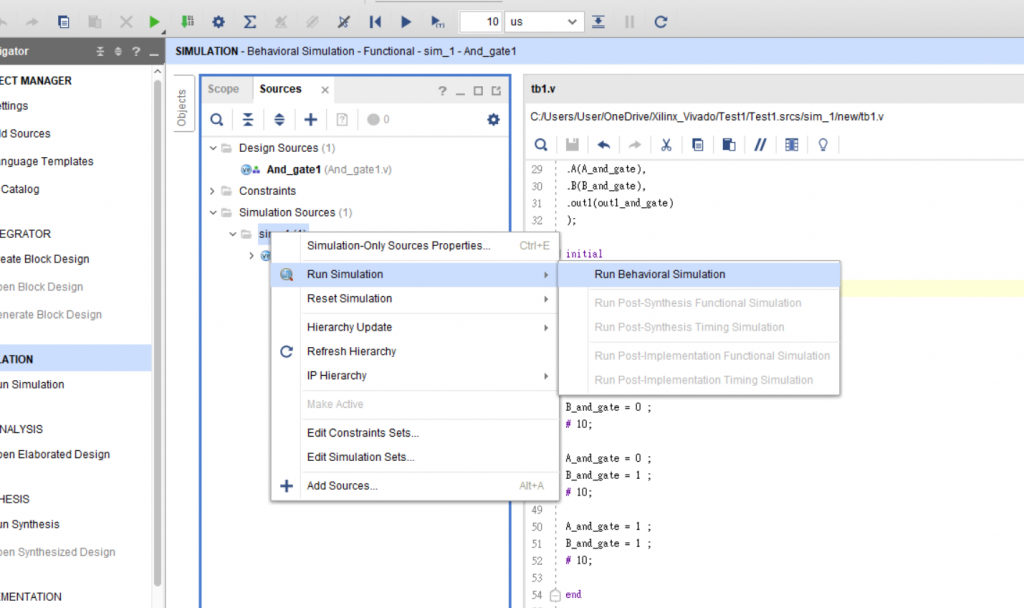

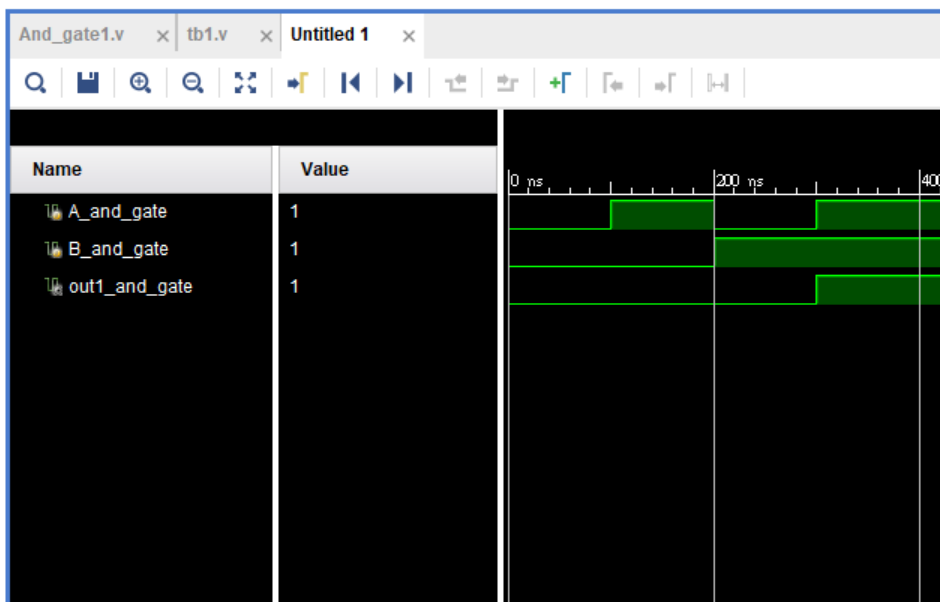

最後進行模擬

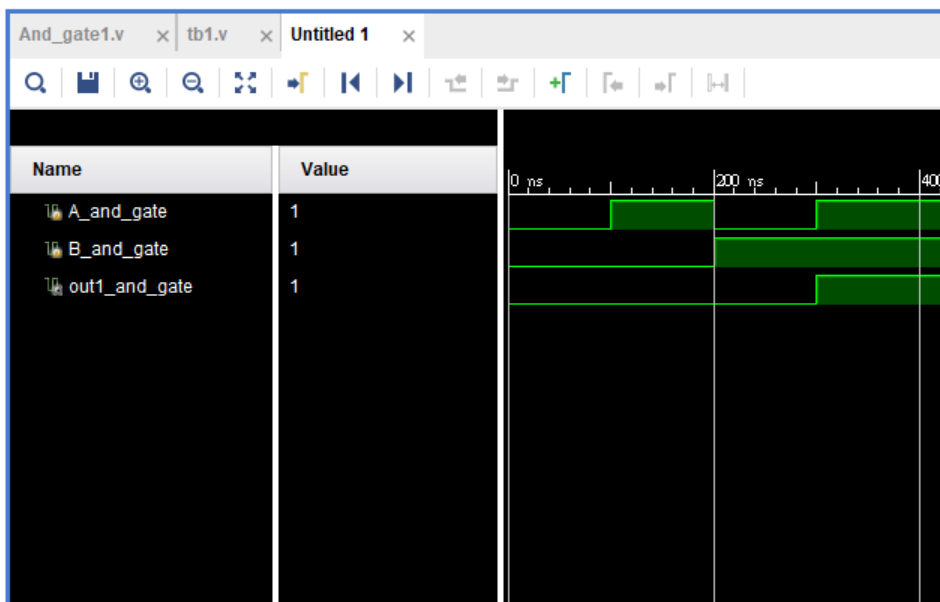

結果就出來了

顯示的結果就是:

好險結果沒問題 哈哈

最一開始的 tb 應該是長這樣

module tb1();

endmodule

Wire 跟 reg

這裡先要講解一個東西 Wire 跟 reg

Wire

Wire你就這樣想它就像是訊號間的連線,Wire不儲存狀態,它的值可以隨時改變

所以我們設定output 為 wire 就是最後輸出將 output

reg

Reg就像是暫存器,reg 的作用類似程式語言中的變數吧?

所以 reg 可以儲存數值

作為參與表示式的運算 (滿常在時序邏輯中出現,類似狀態改變的下一個時序訊號邊沿翻轉時進行)

時序的部分 後面慢慢體會吧

既然是變數用法所以輸入的 A B 就是 reg了喔

我們就定義 3個參數分別是 A B 跟 output

module tb1();

reg A_and_gate , B_and_gate;

wire out1_and_gate;

endmodule

我們要使用And_gate1 所以定義個 And_gate1的function叫 Test_And_Gate

And_gate1 Test_And_Gate

還記得 And_gate1 的function 長這樣 module And_gate1(A,B,Out1);

所以我們將

A 帶入 A_and_gate

B 帶入 B_and_gate

C 帶入 out1_and_gate

And_gate1 Test_And_Gate(

.A(A_and_gate),

.B(B_and_gate),

.Out1(out1_and_gate)

);

module tb1();

reg A_and_gate , B_and_gate;

wire out1_and_gate;

And_gate1 Test_And_Gate(

.A(A_and_gate),

.B(B_and_gate),

.Out1(out1_and_gate)

);

endmodule

timescale

就是 設定 每一個 時間的格子大小 timescale 1ns / 1ps

`timescale 1ns / 1ps

module tb1();

reg A_and_gate , B_and_gate;

wire out1_and_gate;

And_gate1 Test_And_Gate(

.A(A_and_gate),

.B(B_and_gate),

.Out1(out1_and_gate)

);

endmodule

initial

使用 initial 來測試

begin 就像是 C++ 的 {

end 就像是 C++ 的 }

`timescale 1ns / 1ps

module tb1();

reg A_and_gate , B_and_gate;

wire out1_and_gate;

And_gate1 Test_And_Gate(

.A(A_and_gate),

.B(B_and_gate),

.Out1(out1_and_gate)

);

initial

begin

end

endmodule

測試 每 100 秒 變化一次

A_and_gate = 0 ;

B_and_gate = 0 ;

A_and_gate = 1 ;

B_and_gate = 0 ;

A_and_gate = 0 ;

B_and_gate = 1 ;

A_and_gate = 1 ;

B_and_gate = 1 ;

`timescale 1ns / 1ps

module tb1();

reg A_and_gate , B_and_gate;

wire out1_and_gate;

And_gate1 Test_And_Gate(

.A(A_and_gate),

.B(B_and_gate),

.Out1(out1_and_gate)

);

initial

begin

A_and_gate = 0 ;

B_and_gate = 0 ;

# 100;

A_and_gate = 1 ;

B_and_gate = 0 ;

# 100;

A_and_gate = 0 ;

B_and_gate = 1 ;

# 100;

A_and_gate = 1 ;

B_and_gate = 1 ;

# 100;

end

endmodule

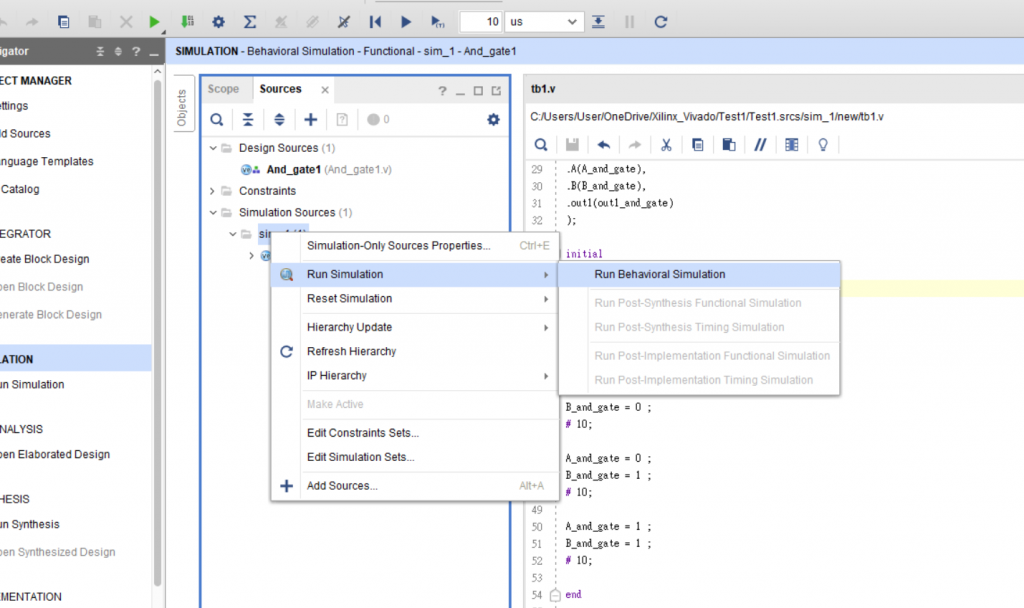

最後模擬看看

看一下結果

這樣就完成的~~ 如果講太快 在跟我反應喔

まあまあか。