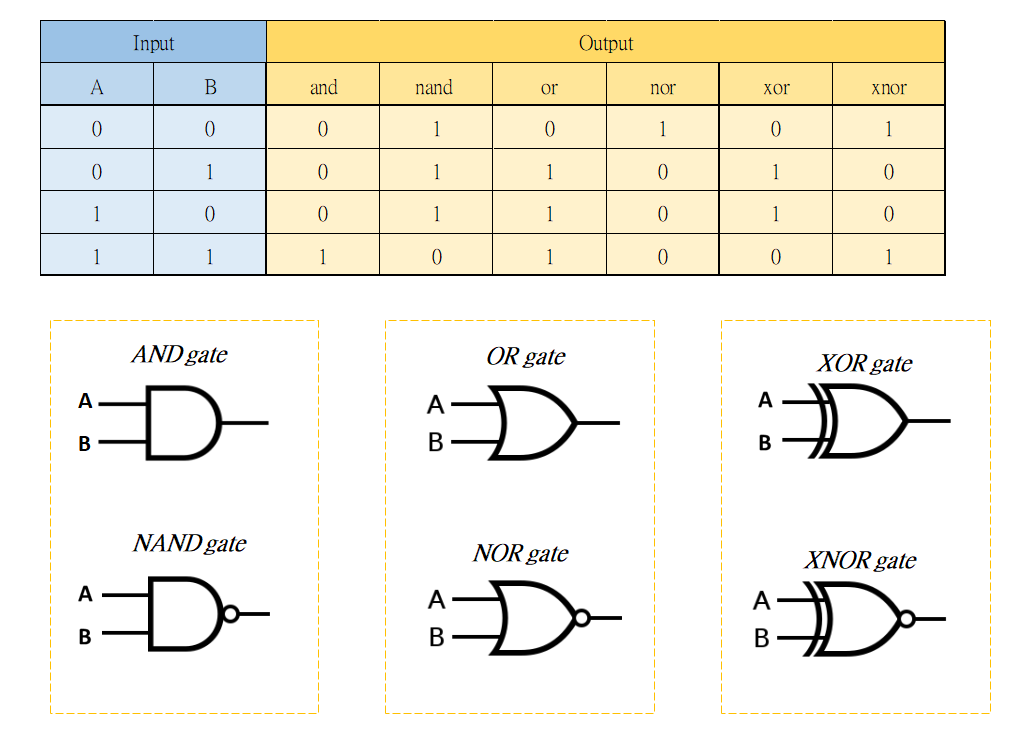

目前講到的 Gate 有6 種

其實 verlog 就有內建這幾個功能

And-Gate → and(output1,input1,input2)

Or-Gate → or(output1,input1,input2)

Xor-Gate → xor(output1,input1,input2)

我們試著用看看這幾個吧

module All_gate1(A,B,Out_and_gate ,Out_nand_gate, Out_or_gate ,Out_nor_gate,Out_xnor_gate ,Out_xor_gate);

input A , B;

output Out_and_gate ,Out_nand_gate;

output Out_or_gate ,Out_nor_gate;

output Out_xor_gate ,Out_xnor_gate;

and(Out_and_gate,A,B);

nand(Out_nand_gate,A,B);

or(Out_or_gate,A,B);

nor(Out_nor_gate,A,B);

xor(Out_xor_gate,A,B);

xnor(Out_xnor_gate,A,B);

endmodule

tb 也簡單寫一下

module tb1();

reg A_in , B_in;

wire out_test_and_gate,out_test_nand_gate;

wire out_test_or_gate,out_test_nor_gate;

wire out_test_xor_gate,out_test_xnor_gate;

All_gate1 Test_And_Gate(

.A(A_in),

.B(B_in),

.Out_and_gate(out_test_and_gate), .Out_nand_gate(out_test_nand_gate),

.Out_or_gate(out_test_or_gate) , .Out_nor_gate(out_test_nor_gate),

.Out_xor_gate(out_test_xor_gate), .Out_xnor_gate(out_test_xnor_gate)

);

initial

begin

A_in = 0 ;

B_in = 0 ;

# 100;

A_in = 1 ;

B_in = 0 ;

# 100;

A_in = 0 ;

B_in = 1 ;

# 100;

A_in = 1 ;

B_in = 1 ;

# 100;

end

endmodule

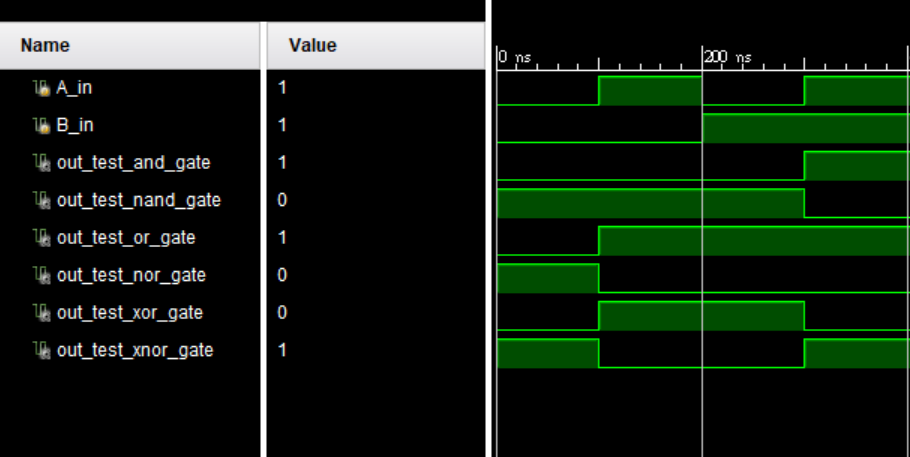

輸出結果看看

and 只有 A=1 ,B=1 會得到1

or 只有 A=0 ,B=0 會得到0

xor A,B相同就是 0

跟預期得差不多