阻隔指定

就是指 具有順序性的信號改變立即更新

輸出信號 = 輸入信號邏輯組合

非阻隔指定

就是指 具有同時性的關係

輸出信號 <= 輸入信號邏輯組合

舉個例子

module Test2_always1(reset,A,B,Out1,Out2);

input A , B ,reset ;

output Out1 , Out2;

reg Out1 , Out2;

reg In1 , In2 ;

always@( A )

begin

if (reset)

begin

In1 = 0;

In2 = 0;

Out1 = 0;

Out2 = 0;

end

else

begin

In1 = ~ B;

Out1 = In1;

In2 <= ~ B;

Out2 <= In2;

end

end

endmodule

程式中的 Reset 為什麼這樣寫 我們之後再講

我們主要看這裡

begin

In1 = ~ B;

Out1 = In1;

In2 <= ~ B;

Out2 <= In2;

end

In1 會等於 ~B 然後 Out1 在等於 In1 ,中間是用 "=" 所以有順序性

In1 數值就是 ~B

Out1 數值就是 ~B

In2 會等於 ~B 同一時間 Out1 等於 In1 ,中間是用 "<="

In1 數值就是 ~B

Out1 數值就是 In1還沒變成 ~B 前的數字

他們兩個同時發生

來測試一下 tb

module tb1();

reg A_in , B_in ,reset;

wire out_o1 ;

wire out_o2;

Test2_always1 test(

.reset(reset),

.A(A_in),

.B(B_in),

.Out1(out_o1),

.Out2(out_o2)

);

initial

begin

reset = 1 ;

A_in = 0 ;

B_in = 0 ;

# 70;

reset = 0 ;

A_in = 0 ;

B_in = 0 ;

# 100;

A_in = 1;

B_in = 0 ;

# 100;

A_in = 0 ;

B_in = 1 ;

# 100;

A_in = 1 ;

B_in = 1 ;

# 100;

end

endmodule

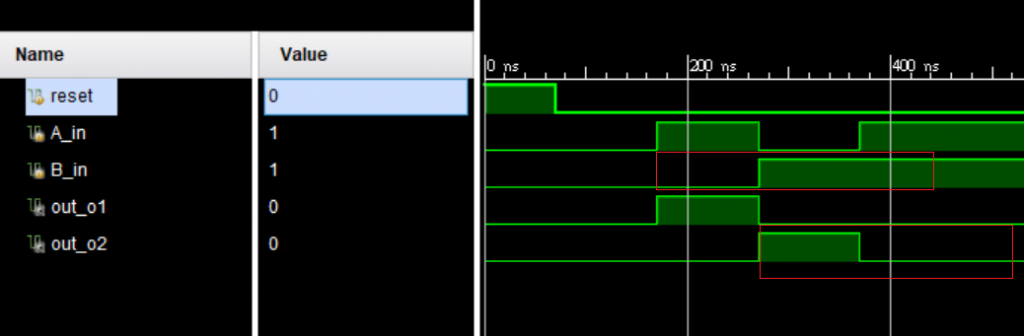

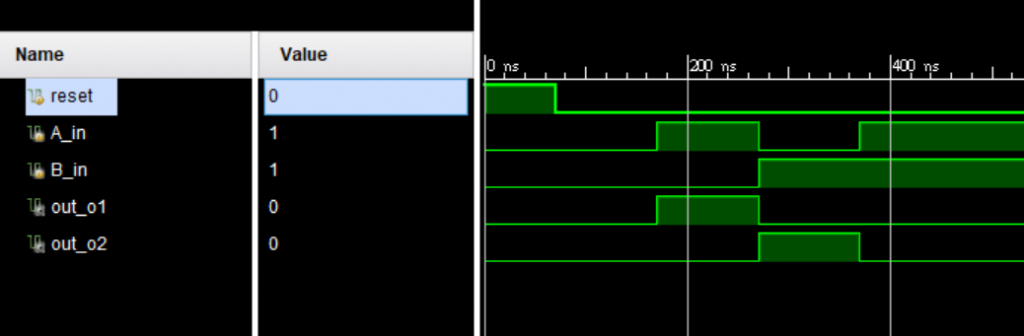

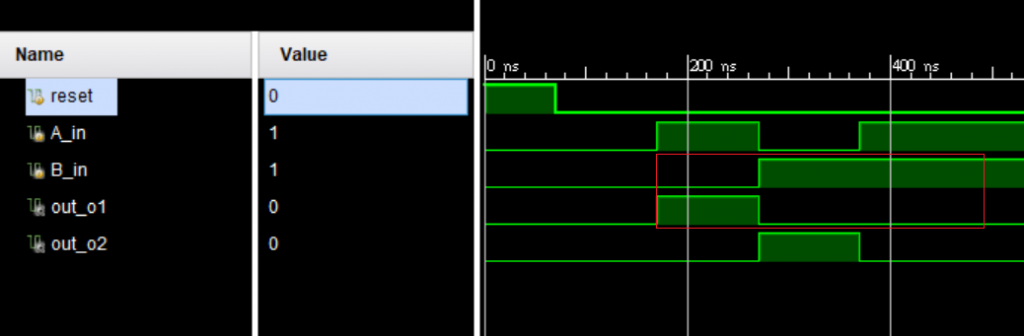

看一下結果

Out1 是 B 的相反

而 Out2 是 B前一個的相反