非阻隔指定

就是指 具有同時性的關係

輸出信號 <= 輸入信號邏輯組合

回到剛剛的範例

module Test2_always1(reset,A,B,Out1,Out2);

input A , B ,reset ;

output Out1 , Out2;

reg Out1 , Out2;

reg In1 , In2 ;

always@( A )

begin

if (reset)

begin

In1 = 0;

In2 = 0;

Out1 = 0;

Out2 = 0;

end

else

begin

In1 = ~ B;

Out1 = In1;

In2 <= ~ B;

Out2 <= In2;

end

end

endmodule

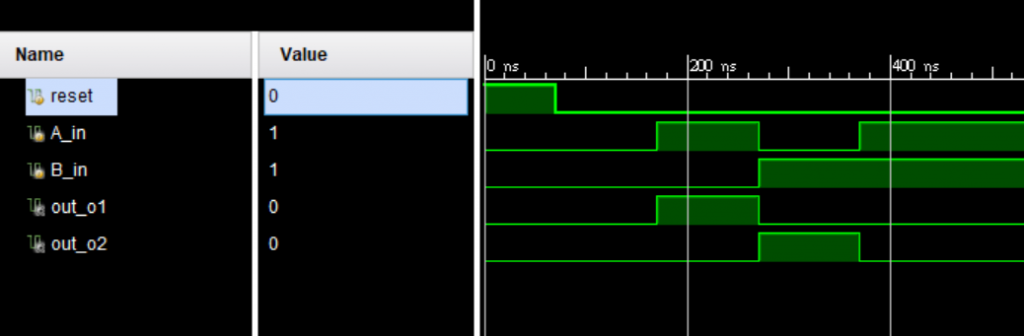

我們可以看到一個 always@( A ) 裡面有一個 reset

if (reset)

begin

In1 = 0;

In2 = 0;

Out1 = 0;

Out2 = 0;

end

reset =1 進入 reset

Out1 、 Out2 都會是 0

為什麼要reset呢? 因為在 reg 打開之前要有一個初始值

如果沒有那一開始的 In2 會沒有數值,那 Out2 對應到的 In2 是沒有數值。

所以 tb 中 一開始有 reset =1 進入 reset 並在這裡初始化數值

initial

begin

reset = 1 ;

A_in = 0 ;

B_in = 0 ;

建議如果在使用 always 每次有寫到 reg 就要記得到 rest 初始化

module Test2_always1(reset,A,B,Out1,Out2);

input A , B ,reset ;

output Out1 , Out2;

/////////////////////////////

//寫到 reg 時 馬上去寫 reset

reg Out1 , Out2;

reg In1 , In2 ;

always@( A )

begin

if (reset)

begin

/////////////////////////////

//馬上去 reset 初始化

In1 = 0;

In2 = 0;

Out1 = 0;

Out2 = 0;

end

else

begin

end

end

endmodule