我們這次來測試 Day 12 的tb1

第1步: Day 12 的程式碼

之前Day 12 的程式碼

module Clk_Add1(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

wire[7:0] Date;

assign Date = Out1+1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=0;

end

else begin

Out1<=Date;

end

end

endmodule

第2步: tb 的參數

我們先寫 tb

幾個簡單的想法

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

endmodule

第3步: Clk作用

寫一下 Clk 執行方式 每 100 格 作為一週期

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

// Clk 執行方式 每 100 格 作為一週期

always #50 clk<=~clk;

endmodule

第4步: initial

寫一下 initial 執行方式

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

// initial

initial begin

end

always #50 clk<=~clk;

endmodule

第5步: 設定 reset

寫一下 reset 在 70格執行

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

// initial

initial begin

reset1 <= 0 ;

clk <= 0 ;

# 70;

end

always #50 clk<=~clk;

第6步: 設定 reset 打開之後

寫一下 reset 打開

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

Clk_Add1 test(

.reset1(reset1),

.clk(clk),

.Out1(Out1)

);

initial begin

reset1 <= 0 ;

clk <= 0 ;

# 70;

reset1 <= 1 ;

# 2000;

$stop;

end

always #50 clk<=~clk;

endmodule

恩恩 大概就這樣

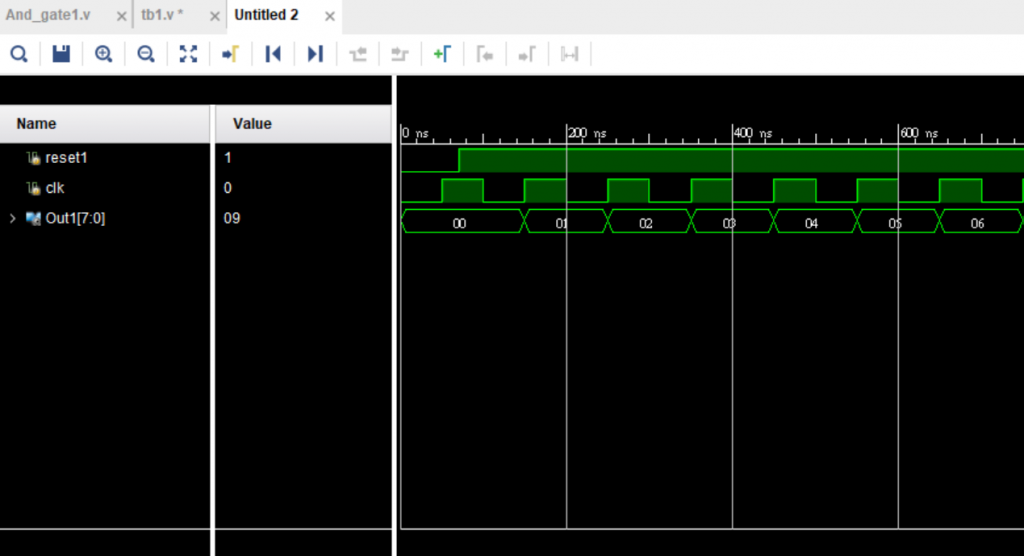

看看結果吧

結果自己來分析看看喔

好了第一關卡通過了 滿簡單的吧

単装砲って、何気にわびさびよね~