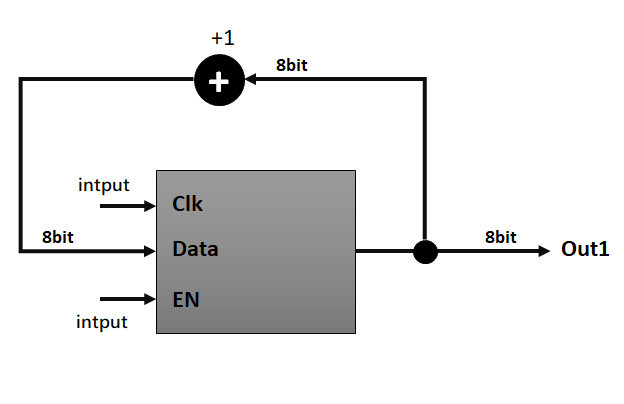

時序組合的電路大概長這樣

第 1 步

簡單想想

我們先從程式 寫來看看

module Clk_Add1(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

endmodule

接下來我們看到 有一個 Data 的線路 而 Data 接到+1

所以 用 assign 來接

assign Date = Out1+1;

module Clk_Add1(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

// 有一個 Data 的線路 而 Data 接到+1

wire[7:0] Date;

assign Date = Out1+1;

endmodule

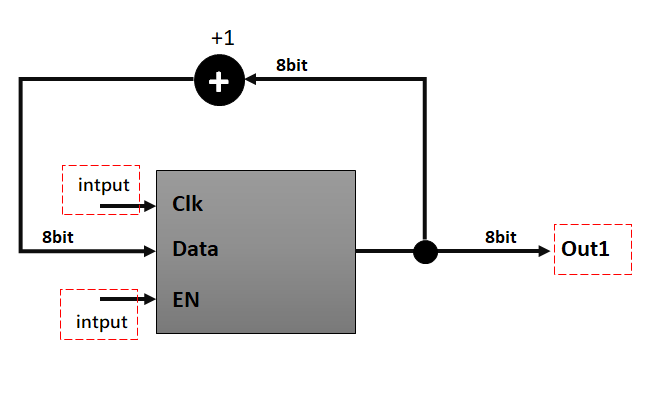

第 2 步

接下來我們有寫 EN是開關

就是初始化,簡單來說 reset 來決定開關

所以就是 reset 觸發 那就出現 always (詳情請看 Day11)

module Clk_Add1(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

wire[7:0] Date;

assign Date = Out1+1;

// 所以就是 reset 觸發 那就出現 always (詳情請看 Day11)

always@(negedge reset1)

begin

if( ~reset1) begin

end

else begin

end

end

endmodule

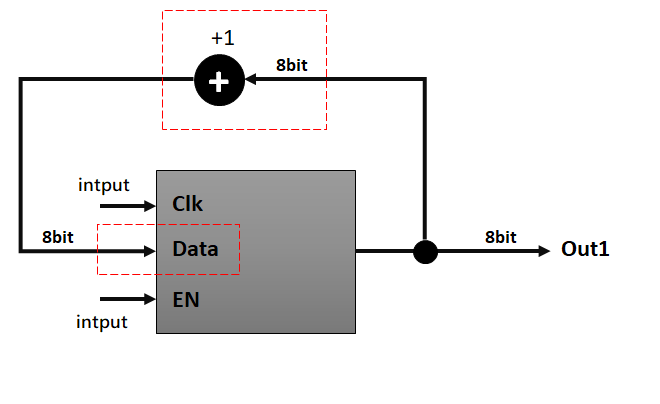

第 3 步

那寫出 reset 而且有 設定 reg 馬上就要初始化 (詳情請看 Day11)

module Clk_Add1(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

wire[7:0] Date;

assign Date = Out1+1;

always@(negedge reset1)

begin

if( ~reset1) begin

// 設定 reg 馬上就要初始化

Out1<=0;

end

else begin

end

end

endmodule

第 4 步

最後加上 clk 觸發 執行 Date 設定在 輸出

module Clk_Add1(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

wire[7:0] Date;

assign Date = Out1+1;

// 加上 clk觸發

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=0;

end

else begin

// 最後將 Date 設定在 輸出 上

Out1<=Date;

end

end

endmodule

OK 這樣應該沒問題吧

ヒトゴーマルマル。まぁねえ。いろいろあったね。でもさ、なんかそれも仕方なかったのかなーってさ。今は思うんだ…。