題目: Rs232的訊號,鮑率我們就設定 115200 ,clk速度 24MHz

現在來寫狀態列表:

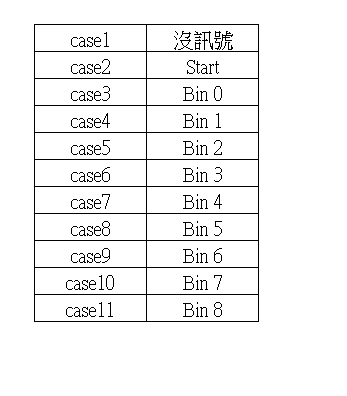

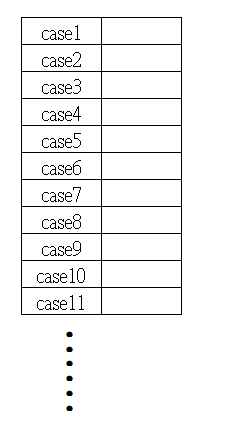

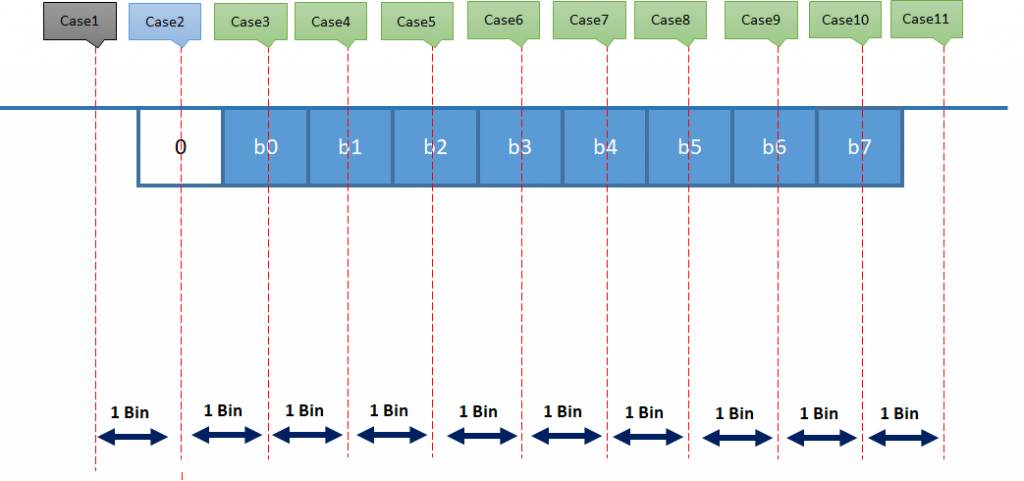

就是 reg 的 Case 的狀態分為

我們先要想要怎麼分圖

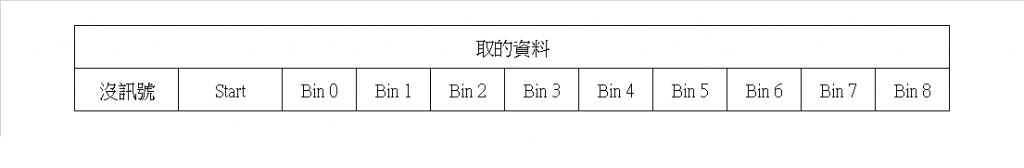

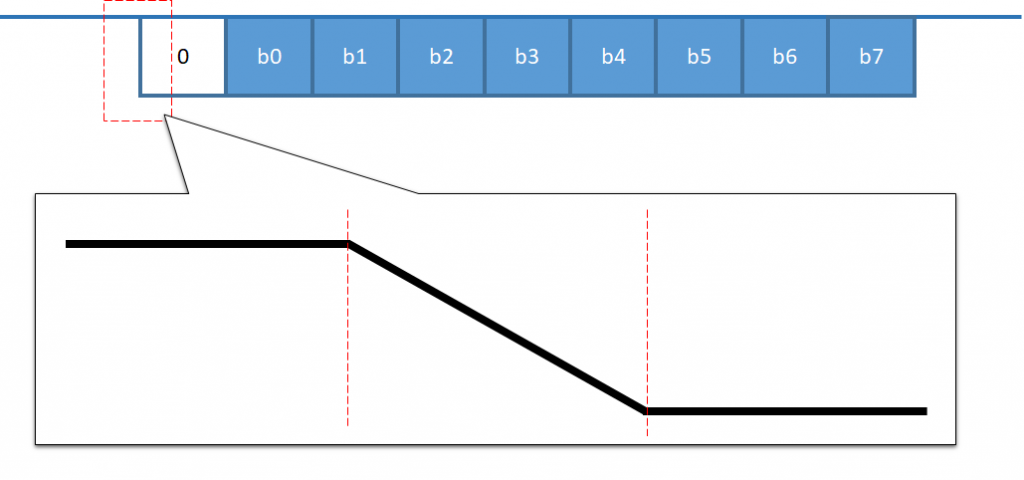

我們收到的資料是:

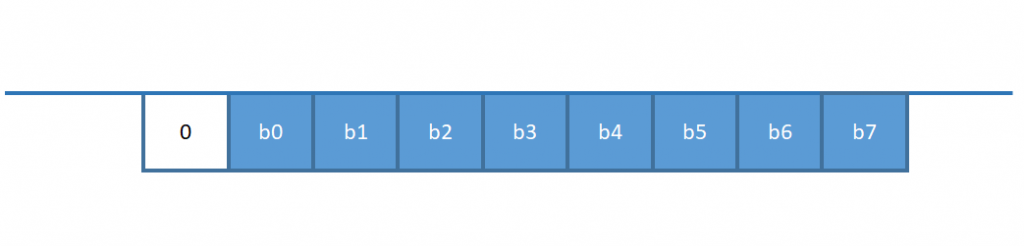

我們先看看,要怎麼取中間的資料

我們總共要取

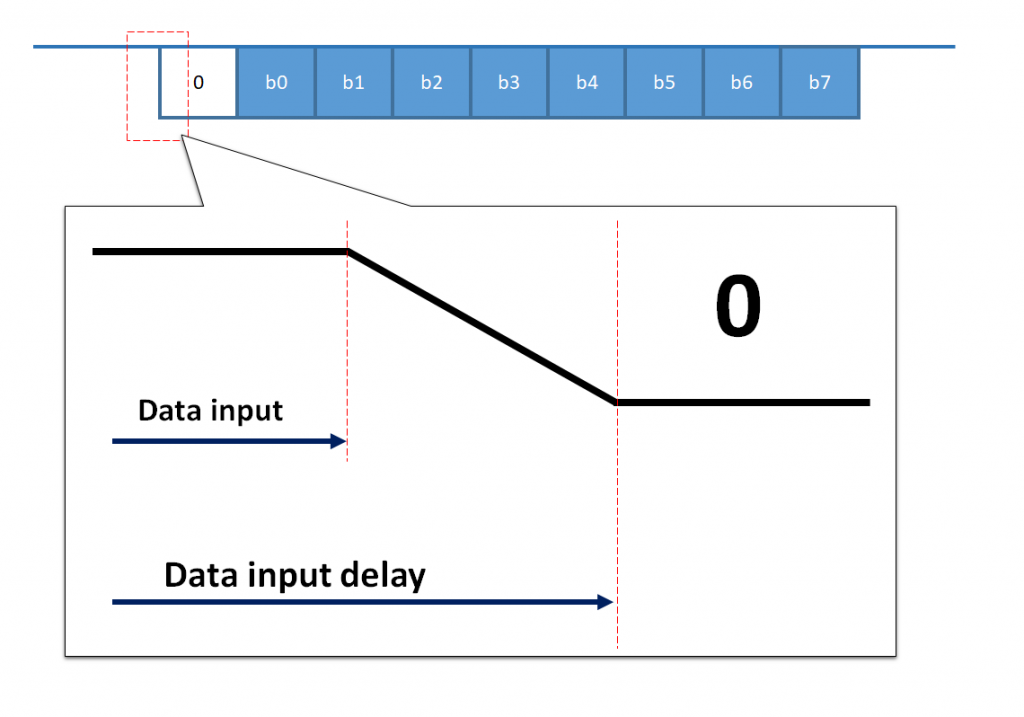

但是害怕資料其實每有這麼漂亮,可能資料有延遲:

延遲圖概念就是 Data input ,但是實際是 Delay之後的事情如圖

Data input Delay之後才輸出資料

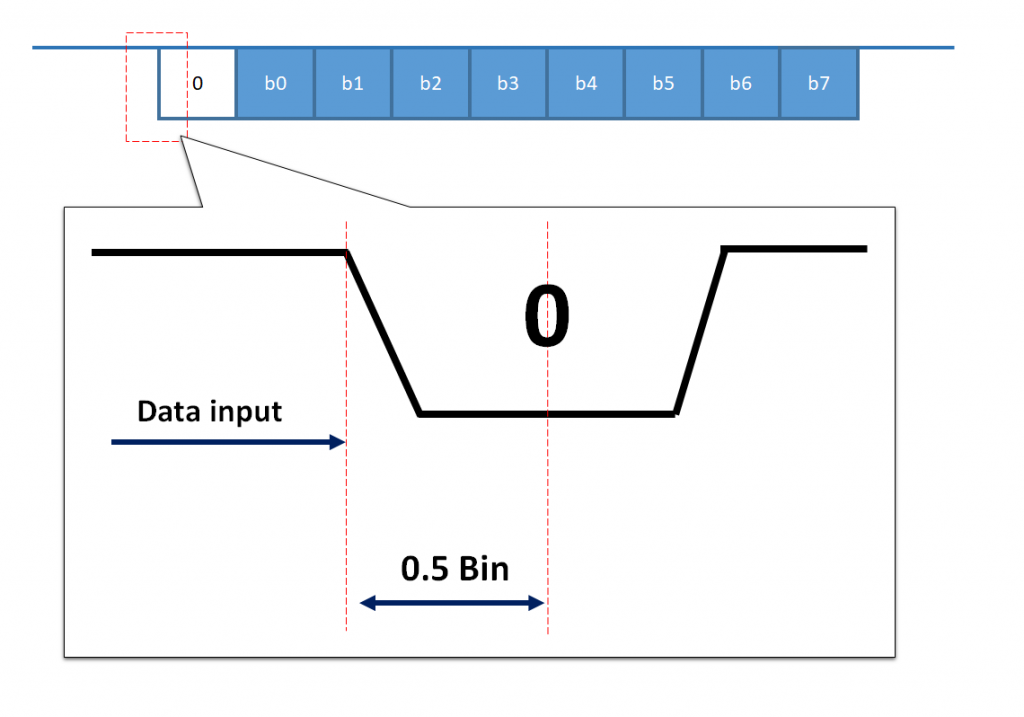

所以我們用要取資料為了保險,就取資料的中間

所以實際的取直方式是:

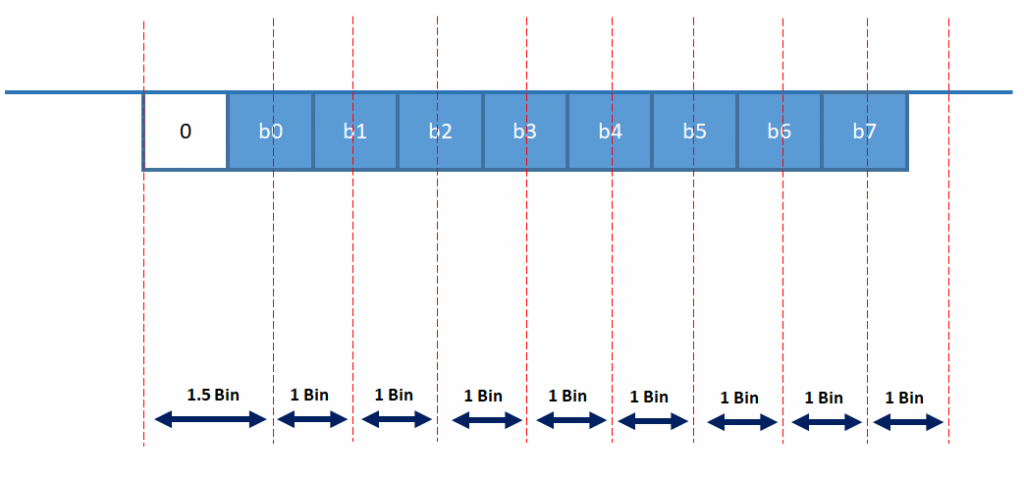

Data input 要取得第一個資料點是 1.5個 bin 大小

因此我們分析實際要拿的位置:

最後我們資料: 列出的case表