選擇 Reg

繼續之前的題目

題目: Rs232的訊號,鮑率我們就設定 115200 ,clk速度 24MHz

其實這題一開始就講到了 Reg 就是 Rs232

設計初始化

我們簡單先初始化設計

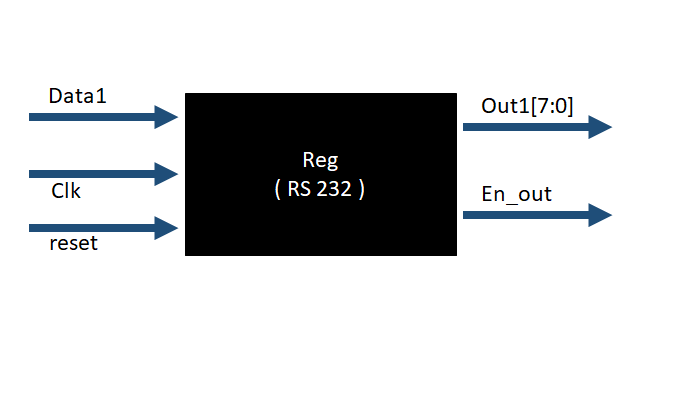

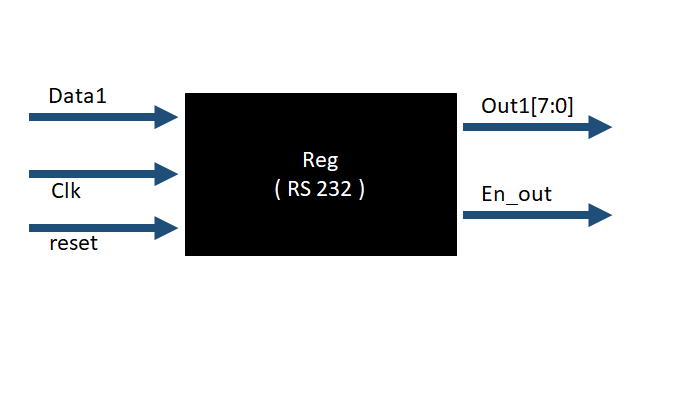

我們先看圖:

初始化第1步 input、output

我們可以看到有 3個 input + 2個output

轉成程式碼:

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

endmodule

初始化第2步 always

由圖知道這是個有 Reg的程序,不會只用到 assign

所以我們加入 always作設定

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

always@()

begin

end

endmodule

初始化第3步 always clk 觸發條件

我們設定 clk在 posedge 時觸發,Clk 爬起來瞬間觸發

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

always@( posedge clk)

begin

end

endmodule

初始化第4步 always reset 觸發條件

reset 是作為 Reg還沒開機時設定 ,還有初始值的功用

因此設定Reg 進入 Low時 觸發開始執行

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

always@( negedge reset1 or posedge clk)

begin

if( ~reset1) begin

end

else begin

end

end

endmodule

初始化第5步 case 的狀態分析

我們這次 reg具有不同的狀態,因此將 case加入

而Case 分辨的狀態叫 State 具有記憶所以設定為 State

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

reg[7:0] State1;

always@( negedge reset1 or posedge clk)

begin

if( ~reset1) begin

end

else begin

case (State1)

0:

begin

end

1:

begin

end

default:

begin

end

endcase

end

end

endmodule

初始化最後一部 將設定的 Reg 初始化

一看到 Reg 立刻就要在 reset 初始化

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

reg[7:0] State1;

always@( negedge reset1 or posedge clk)

begin

if( ~reset1) begin

State1 <=0;

end

else begin

case (State1)

0:

begin

end

1:

begin

end

default:

begin

end

endcase

end

end

endmodule

這樣就初始化完成了

下一次開始我應該就不會寫初始化流程