Verilog 是由一個一個模組 (module) 堆疊起來的,而最上層的模組 (top module) 與 C 語言的主函式 (main function),將作為整個電路的起點。

在開始實作 Verilog 之前,我們會先把架構圖畫出來。這個架構圖會把各個模型的關係建構出來。

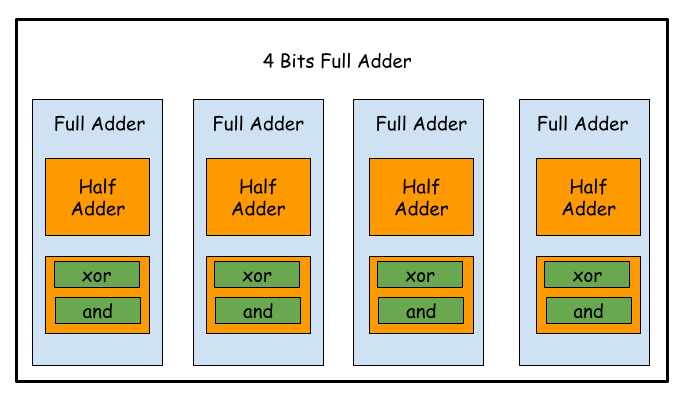

如下圖為一個四位元全加器的架構圖,從這張圖我們可以清楚知道

如此一來,我們可以更有架構的去完成 Verilog 的程式實作,而不是將所有程式碼都集合於 top-module 中。

Verilog 其實有一點物件導向的意味在,我們會先生成模組 (module),而大模組的組成會依賴小模組生成的物件。這不就是物件導向的 class 和 object 之間的關係嗎?