比起畫硬體結構來看,Verilog 算是個程式語言,我個人覺得裏頭的概念有平行程式(因為電一來全部的模組都會開始動起來)、物件(可以把元件模組化,甚至以參數的方式實體化)。

說到底,Verilog 的最終目的還是生產出硬體,而最後生產的步驟可能要價非凡,因此,越早發現錯誤甚至是能進行大量測試模擬是在好不過的事了。所以 Verilog 大概可以分為兩大塊:設計(Design) 和 驗證(Testbench) 。(請見下圖)

在軟體設計時,我們都會產生一些測試資料來驗證軟體的正確性;同樣的,在 Verilog 裡做驗證的叫做 Testbench ,餵給設計好的東西輸入,並收集他的結果比對看正確性如何。是說,這個 Testbench 也是用 Verilog 來寫的噢!只是比起 Design 部分的 Verilog 限制較少,可用的語法又更多、自由一些。

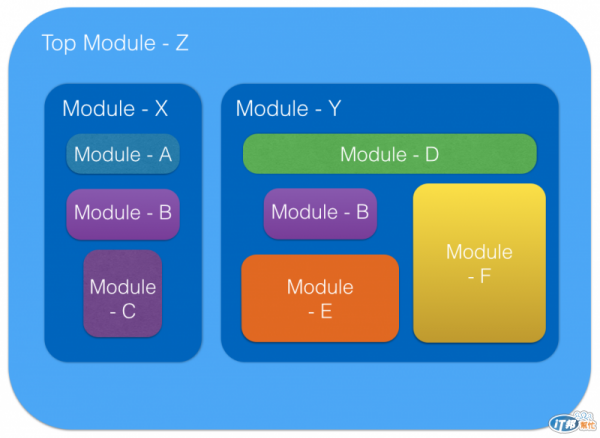

那我所謂的物件又是怎麼一回事呢?(請看下圖)

整個設計裡,最大的、包括全部的那個模組 Z 會被稱為 Top Module 最上層的模組,就好比像是樹的 root 一樣;接著,在模組裡頭又可以包含多樣不同的子模組,如此遞迴下去。

而模組並不是說每一塊一定要獨一無二,有些重複功能模組可以被提煉出來成為常用的規格,比如說裡頭的 Module-B 可能是一個 F/F, Full Adder 之類的。在要使用的時候就像物件初始化一樣,把該接的東西接上去,就可以產生一個實體出來了。

不過如果在很多模組裡有很多的子模組,那要怎麼去區分個別呢?這時候就會用類似階級(Hierarchy)的方式才分別。比如說我想看 X 裡面的 B ,那就是 Z.X.B 來取得,如果是 Y 裡頭的 B 則是 Z.Y.B 這樣。要記得噢~這個方式在之後要去觀察某個特定的東西時很方便噢!

那麼,今天就講到這邊吧~

hydai@差點早睡睡過發文時間