MUX 是很常見的東西,通常在選擇的時候都會有他的身影,先簡單介紹一下它的功能(以 1-bit 為例子):

_______

A --------| MUX |

B --------| | -------- Output

--------

|

Select --------|

會有一個訊號叫做 Select 用來選擇 Output 是要接哪一個輸入端, A, B 分別是 Input 的來源。如果今天 Select 的訊號為 0 ,那我們就把 A 的訊號送到 Output 端去;否則 Select 的訊號為 1 時,就把 B 的訊號送到 Output 端去。

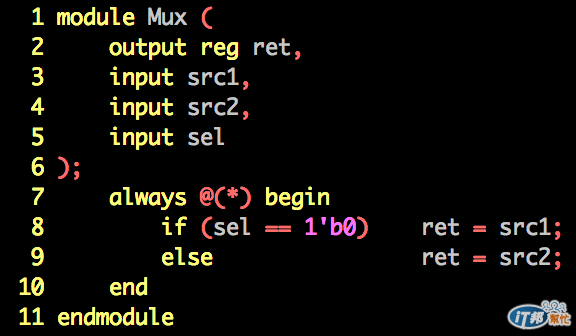

那 Verilog 程式碼會長什麼樣子呢?

Line 1 & 11 代表了這個叫做 Mux 的 module 的範圍,由關鍵字 module 為開頭,endmodule 作為結尾。

Line 1, module 後面的 Mux 就是這個 module 的名字,可以自定。

接著 Line 1~6 被兩個小括弧夾住的地方就是宣告輸出入的地方(內容後面再解釋)。

在 Line 7~10 的部分,則是最關鍵的判斷與選擇的地方,是被一個 always block 所包圍的,通常要做事的東西會被包進這個 block 裡頭。

注意到輸出入的列表,有幾個型別,input, output, reg

input 顧名思義就是輸入,

output 也如你所想的是輸出,

reg 呢?如果這個變數在 always block 裡頭需要去動它的話,就要宣告成這個型別,並不代表最後一定會合成出一個 reg 出來噢!!!

其實還有一個叫做 wire 的型別,沒有被宣告成 reg 的就會被當成 wire ,所以我們上面所寫的 input 事實上是 input wire src1 這樣

還有一點,在 Line 8 看到的 1'b0 就代表了 1 bit 的 0 ,如果變數沒有宣告長度的話,預設就是 1 bit。但是常數如果沒有加上長度的話會被當成是 32 bits 噢!

always block 的部分,這邊先講個大概,我們明天還會講更詳細一些。

@(*) 的意思是當我 always 裡頭的訊號有變動時,就會去執行。

if-else 的部分,就是用來選擇的,條件裡可以用 == 代表相等, >, <, <= , >= 等來比較。

要指定值得時候,因為這裡還沒有 clock 進來,所以用 = 來給值。

ret = src1; 就是把 src1 的值給 ret。

今天就先到這裡吧~不然就要過十二點GG啦~

hydai@快趕不上的鐵人賽