您好,2018! 起個大早繼續來奮戰!

然後呢,突然發現,應該下個更聳動的標題之類的!!

本篇主要是講一下底層硬體的細節XD!!

不過由於我也不是相關背景出來的,算是邊做邊看邊學吧!

如果有錯誤的話,請在底下留言的地方提出 有毒。請小心服用!

感謝!

本日的主題內容如下:

一樣先來講古 複製+貼上

JTAG是聯合測試工作群組(Joint Test Action Group)的簡稱,是在名為標準測試存取埠和邊界掃描結構的IEEE的標準1149.1的常用名稱。此標準用於測試存取埠,使用邊界掃描的方法來測試印刷電路板。

....中間省略

在設計印刷電路版時,目前最主要用在測試積體電路的副區塊,而且也提供一個在嵌入式系統很有用的偵錯機制, **提供一個在系統中方便的"後門"** 。當使用一些偵錯工具像電路內模擬器用JTAG當做訊號傳輸的機制,使得程式設計師可以經由JTAG去讀取整合在CPU上的偵錯模組。偵錯模組可以讓程式設計師偵錯嵌入式系統中的軟體。

---引用自Wikipedia - JTAG

巴拉巴拉好複雜...... 剩下請自行觀賞Wikipedia上面精美的介紹!

另外提供一個當初我在學習的時候,參考了幾份文件中,

我覺得寫得還不錯的網站,寫得蠻淺顯易懂的:

小蘿蔔工作室 Little Robot Studio - JTAG

在上面的網站中還有個不錯的範例--讀取 IDCODE,

簡單的來說,從軟體的角度來看的話,就是先對IR(instruction

register)寫入要執行的動作,然後再從DR(data register)讀取出對應的資料!

詳細的步驟,我覺得上述網站中,已經把基本上JTAG的運作過程講得非常清楚,

還請各位多多參考上面的網站!

本文還是主要關心在RISC-V中的JTAG Debug Transport Module是如何設計和使用!

JTAG Debug Transport Module主要的輸入為JTAG的訊號,並依照對應的操作,

回傳上層Debugger所需要的資料,或是轉發給底層Debug Module去做更進一步的處理!

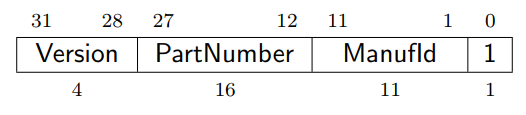

根據JTAG的設計,除樂"IDCODE"和"BYPASS"為必要有的部分,其餘可以由硬體設計者自行規劃,底下會介紹到JTAG Debug Transport Module其他會用到的Registers和其定義!

---引用自RISC-V External Debug Support 0.13

主要分成以下三種欄位:

另外就是JTAG IDCODE有個特點,LSB的地方必定為"1",這蠻有趣的!

留給讀者自行想像一下為啥要這樣設計!

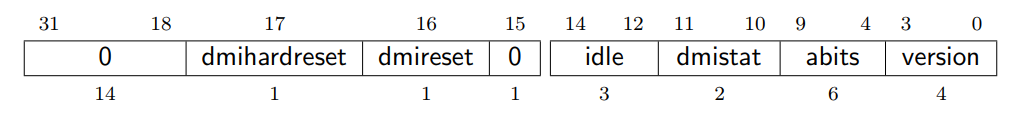

---引用自RISC-V External Debug Support 0.13

這個Register主要是Debug Transport Module的控制和獲得狀態用,主要欄位如下:

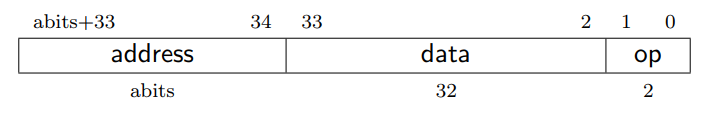

假如Debugger需要Debug Transport Module將資料送至更底層的Debug Module時,就對這個$dmi Register寫入,格式如下:

---引用自RISC-V External Debug Support 0.13

另外op也當作狀態使用,Debugger需要自行讀取op,並判斷動作是否完成:

(*註1) 忘記常用的Debug Module的Register的話,可以在「Day 10: RISC-V Debug Module (下篇)-Debug Module Registers」這邊複習一下!

---引用自RISC-V External Debug Support 0.13

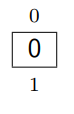

這是個1-Bit的Register,假如JTAG上面有很多的TAP串起來,

這個目的就是告訴該TAP不要有任何動作!

基本上這邊的操作比較瑣碎一些,尤其是跟硬體溝通的部分!

需要花更多精神來判斷傳輸是否完成,是否需要重做,還有資料的處理等等繁瑣得事情~

然後...... 明天要上班了,所以.....

我把實作的部分拆成下一篇.........XDDD

2018/01/08 Fixed typo