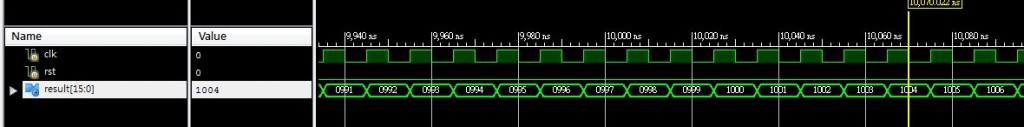

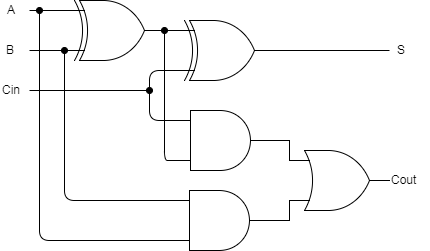

今天要來分享BCD計數器,如果對BCD不瞭解的人可以參考一下維基百科,我們先來看一下原本1-bit加法器的構造

所以如果你寫一個a = b + c的運算,會根據你的bit數去用1-bit加法器組成,

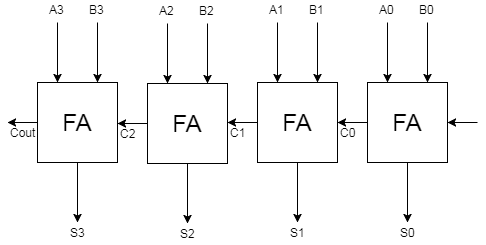

像上圖這樣,如果是4bit的運算就會用4個加法器組起來,像上圖這樣,1-bit的加法器會包成一個module,所以今天我們要做一個BCD計數器就是要模仿加法器的做法,先做出十進位的BCD計數器去組出四位元的BCD計數器.

十進位BCD計數器:

module BCD(

input clk,

input rst,

input Cin,

output reg[3:0]sum,

output Cout

);

always@(posedge clk)begin

if(rst)

sum <= 0;

else if(Cin)

sum <= (sum == 9) ? 0 : sum+1;

end

assign Cout = (sum == 9 & Cin);

endmodule

利用十進位BCD計數器組出從0計數到9999的BCD計數器:

module BCD_counter(

input clk,

input rst,

output [15:0]result

);

genvar i;

wire Ci[3:0];

wire Co[3:0];

assign Ci[0] = 1;

assign Ci[1] = Co[0];

assign Ci[2] = Co[1];

assign Ci[3] = Co[2];

assign result = {sum[3],sum[2],sum[1],sum[0]};

wire [3:0]sum[3:0];

generate

for(i=0;i<4;i=i+1)begin

BCD

B(

.clk(clk),

.rst(rst),

.Cin(Ci[i]),

.sum(sum[i]),

.Cout(Co[i])

);

end

endgenerate

把十進位的BCD計數器複製四份,並把input output接好,包括進位等等的訊號線,接下來就能跑模擬看結果了,因為沒有其他input,所以testbench只要給clock訊號就可以work了.