昨天談完Implementation之後,今天來談談timing的問題,當timing violation時,原因大多分為set up time violation,跟hold time violation,有興趣的朋友們可以去看一下維基百科或是其他更詳細的解說,這邊對這兩種violation做一個簡單的解釋

Set up time:clock上升前,存進暫存器前需維持一段穩定的時間,才能保證存進暫存器的值沒有問題,這段需維持穩定的時間就稱為set up time.

Hold time:clock上升後,暫存器的值需穩定一段時間,才能保證傳到下一層時的值是正確的,這段穩定的時間就稱為hold time.

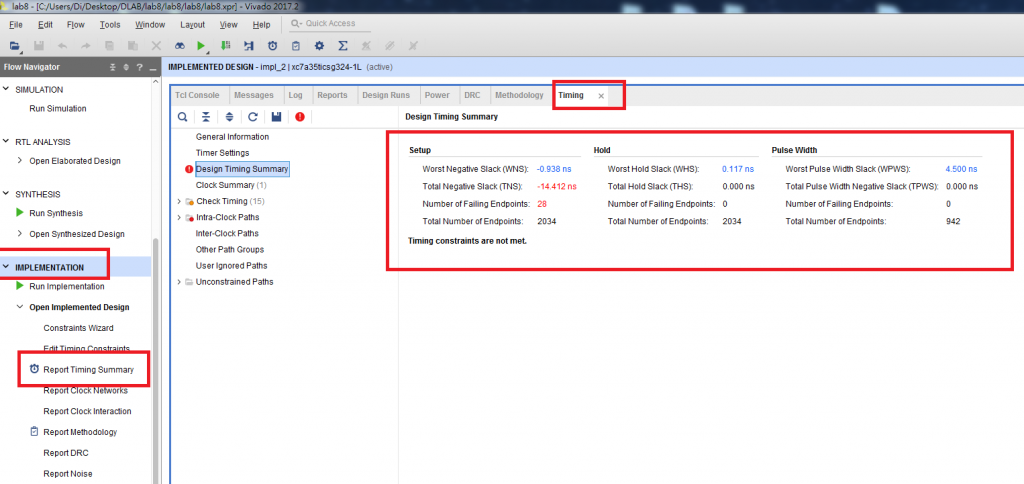

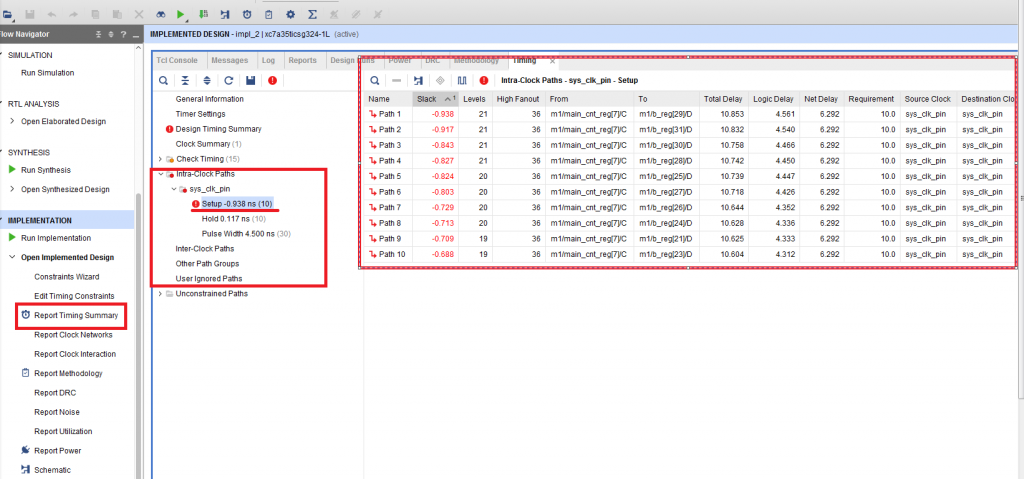

通常在single source clock時,比較會出問題的是set up time violation,遇到hold time violation時,可以加幾個buffer緩衝即可,set up time violation通常比較難克服,一般來說是因為運算太複雜導致時間內算不完才會有這問題,今天這邊舉vivado如何看timing有沒有violation.

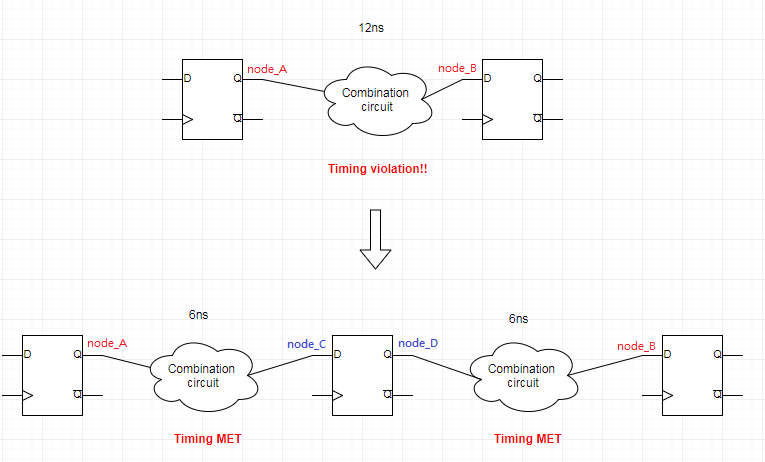

如果遇到set up time violation的話,最簡單的方法就是根據violation的資訊找出有問題的path,然後多加一層register進去,下圖為示意圖.

會遇到timing問題的通常就像上圖,combination運算太過複雜,一個clock做不完的邏輯運算,所以要拆成兩個clock去運算,就像上面這樣,原本的邏輯運算需要12ns,如果run在100MHz(10ns)的clock rate的板子下就會有timing violation,所以找到問題的path,在中間多加一個register進去

always@(posedge clk)begin

a <= b * c * d;

end

像上面這例子,如果一次做兩個乘法運算遇到timing問題的話,就可以把兩個乘法問算拆成兩個clock去做.

always@(posedge clk)begin

temp <= b * c;

end

always@(posedge clk)begin

a <= temp * d;

end

雖然這方法能有效解決timing問題,但會影響performance,就上上面的例子,原本預計一個clock就算玩的東西突然要變成兩個clock,效率突然降兩倍,所以明天會再介紹其他幾種不一樣的方式解決timing問題且比較不影響效能的方法.