今天想來跟大家聊聊low power design,為什麼power comsumption會這麼重要呢,先來想一下,假設設計了一顆處理器,沒有考慮功耗的話,使得設計出來的處理器功耗非常高,浪費電是其次,但一顆功耗高的處理器會造成溫度過高,好的話只會將performance降低,不好的話可能整顆處理器燒掉連帶影響週邊設備,所以一顆功耗高的IC其實也是一個不定時炸彈,

大家都有聽過莫爾定律吧,隨著製程的進步,同樣面積大小的IC能擁有越來越多的standard cell,就以處理器來說,雙核心的處理速度不會比同項目的單核心速度快兩倍,但為什麼會往多核心發展,就是因為再製成先進的情況下,單核心的速度越來越快,相對的功率消耗越來越高,導致溫度上升是指數成長的現象,所以避免溫度過高的情況下,就選擇以多核心的方式取代多核心,即使效能會降低的情況下.

再舉一個例子,如果是一個提供給醫療電子的IC,像是生命維持儀器的IC,需放在心臟旁邊供給能量,需要裝這項儀器的通常為年老的人,假設說這個醫療電子功耗非常高,導致使用的人年年都需要開刀更換電池,你能設想對使用的人負擔有多大,若換成低功耗的設計,變成十年才需換一次電池,這樣造成負擔相對小很多.

以上的例子就能明白功率消耗是一個非常重要的問題,那怎樣才能設計一個低功耗的電路呢,我們先來探討功率的種類.

static power:為漏電流所產生的功率消耗,為電晶體非工作情況下所產生的電流稱為漏電流,隨著製程越來越先進,漏電流所產生的功耗也逐漸逼近或超越dynamic power,但這邊就不多加討論.

dynamic power一直以來都是功率消耗最多的項目,指每一個邏輯閘0變1或1變0所做的充放電消耗的功率,所以減少switch情況就能減少一部分的dynamic power,今天就針對dynamic power來做分享吧.

在design flow底下,當verilog code完成後,tool在作最佳化的過程的當中也會對功率消耗做優化,但是能做的非常有限,所以在要做一個low power design時,其實就要從最一開始的演算法設計了,那今天我們從verilog code level來看.

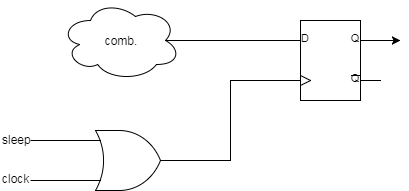

首先先來觀察一下,在寫一個循序邏輯電路時,是不是每一個always block都有一個posedge clk,clock也是一個dynamic power consumption的原因之一,如果說當邏輯閘沒有要變化時,我們把指定的always block的clock凍結起來不要讓他震盪,也是low power方法之一,稱為clock gating,

上圖為簡單的示意圖,sleep為你要凍結的時機,為1時flip-flop就不會變值,這樣一來就能節省部分的dynamic power.

介紹完clock gating之後,大家應該有發現,要做low power就是邏輯閘減少變化的次數,所以使用FSM也是可以做lower power,在某些state做運算,其他state就維持不變,一個較好的習慣是在else項目寫自己等於自己,如下:

always@(posedge clk)begin

if(state == s1)

a <= a+1;

else

a <= a;

end

再來就是,面積用得少,功率消耗自然就少,所以經驗也很重要,好的coding stytle更為重要,low power也是一門非常大的學問,IC設計的low power論文近期更是為多,短時間也是講不完,所以今天也只是淺談一部分,往後有機會看到有趣得再跟大家分享囉.