最近幾年來在,熱門的電路實作方式中主要分為FPGA以及ASIC,那今天就來聊聊ASIC以及FPGA的差異以及個別的優勢.

首先先來看ASIC,特殊應用積體電路(Application-specific-integrated-circuit),

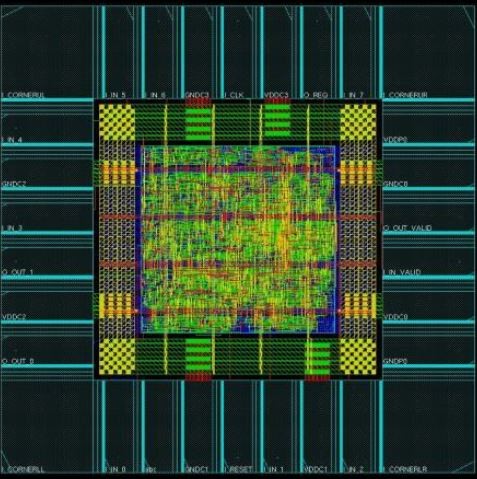

是一個依據需求所客製化的IC,設計流程較為FPGA麻煩,寫完verilog後要經過一連串的模擬與驗證,最後才能下線生產晶片.

上圖為ASIC在實作過程需經過一連串的模擬及驗證示意圖,而且一旦生產晶片後就不能再更改應用的功能,但好處是因為是客製化,所以同樣的功能速度可以快FPGA好幾倍,而且大量生產下也較為FPGA便宜許多,

相反的FPGA為現場可程式化閘陣列(Field-Programmable-Gate_Array),顧名思義是可重複燒錄指定應用的電路到板子上,因為可以重複燒錄到板子上,所以模擬和驗證就沒ASIC這麼重要,錯了就重改完在燒一次,並不會像ASIC一下晶片就回不去了.

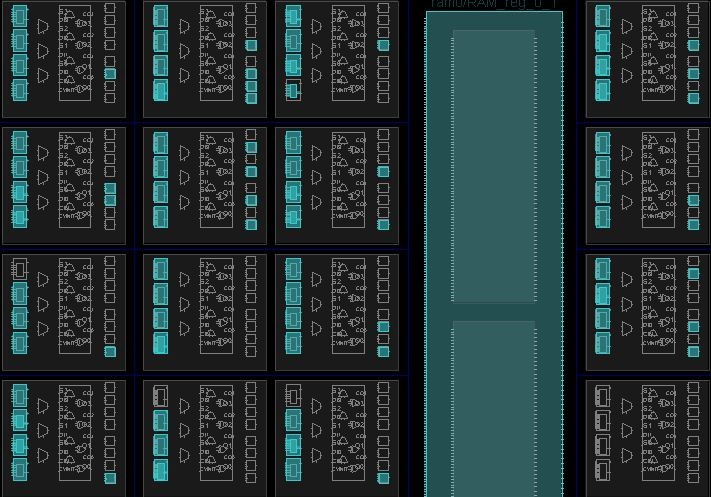

流程就像前幾天介紹過的implementation,FPGA板子裡面大量的邏輯閘都是擺放在固定的的位置,當完成一個指定電路後,經過tool優化後會挑出板子上部分資源來實現你的電路,但又因為全部的資源都固定在板子上,包括flip-flop,and-gate,or-gate,甚至是clock tree等等,所以同樣的電路因為擺放位置的限制,速度才遠低於asic,畢竟asic是完全根據電路需求去做最佳的客製化,尤其是routing的部分,如果tool演算法不夠聰明就有可能因為太複雜繞線繞遠路,看合成報告時,常常繞線的時間多於邏輯運算時間很多,邏輯閘的擺放位置也是,因為不能做擺放位置的更改或者是compress.

上圖為FPGA內部的邏輯閘分佈圖,可以看到就像我所說的,各個邏輯閘都是擺放在固定的位置,會造成效能上的限制,這就是為什麼速度上會跟asic有這麼大的差距,但是好處就是可以重複燒錄,今天做編碼器,明天做解碼器,又或者做顆處理器,非常有彈性,但也較為ASIC昂貴好幾倍.

今天談的都只是ASIC跟FPGA的冰山一角,但還是做點小小的總結,以量產來說,ASIC價格絕對比FPFA低非常多,速度ASIC也比FPGA快許多,但FPGA優點就是可以重複燒錄,可以可以實作不同的電路及驗證,非常適合拿來教學用或者是下晶片前的一種驗證方式,至於ASIC比較偏大量生產的消費電子,這邊就分享給大家.