今天先教大家安裝會用到的工具,如果有玩過FPGA應該都知道Xilinx這間公司,我們要用的工具就是Xilinx所提供的Vivado 2017.3這套軟體,因為這一系列的教學比較著重於行為正確性,大多的教學只需要跑模擬就好,所以如果你有其他可以跑電路模擬工具的話(ex: ModelSim)也可以用自己習慣的工具,不用特地下載Vivado沒關係,以下是安裝步驟,安裝完會簡單寫一個程式驗證工具軟體是否有安裝成功。

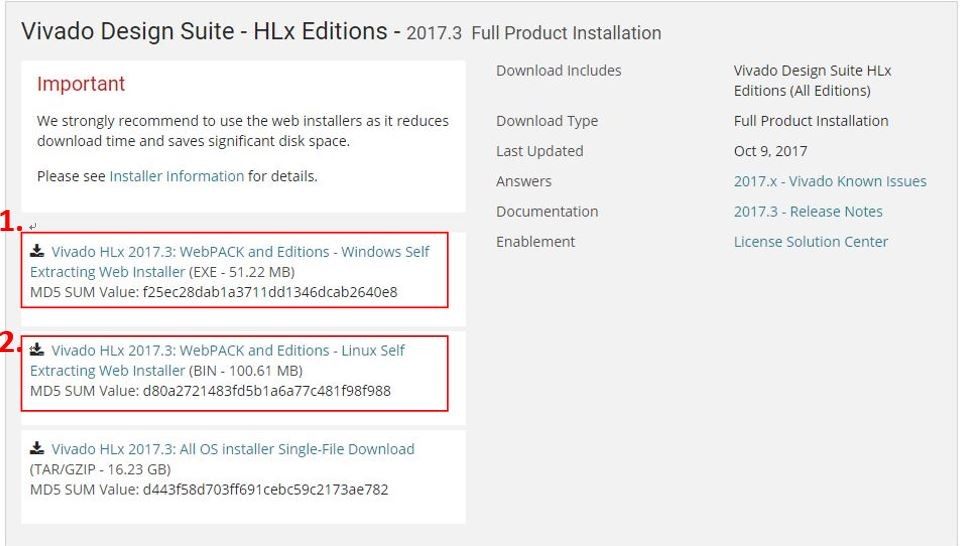

步驟一 先到Xilinx官網下載Vivado 2017.3,就根據作業系統下載,如果是Windows就下載第一個選項,Linux就下載第二個選項,開始下載安裝檔之前可能要你註冊一下帳號,大概花個5分鐘去註冊,之後就能繼續下載了。

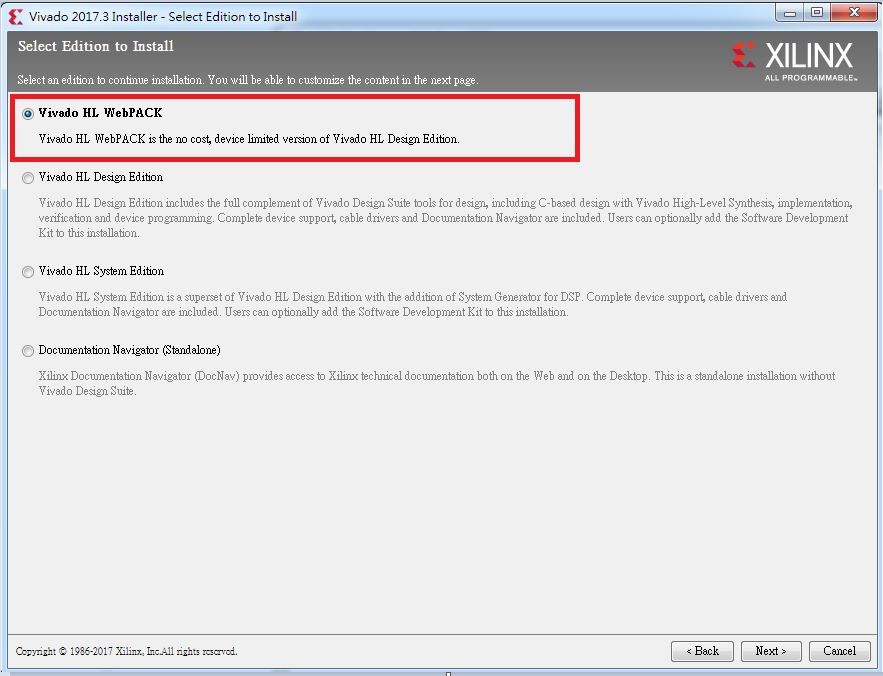

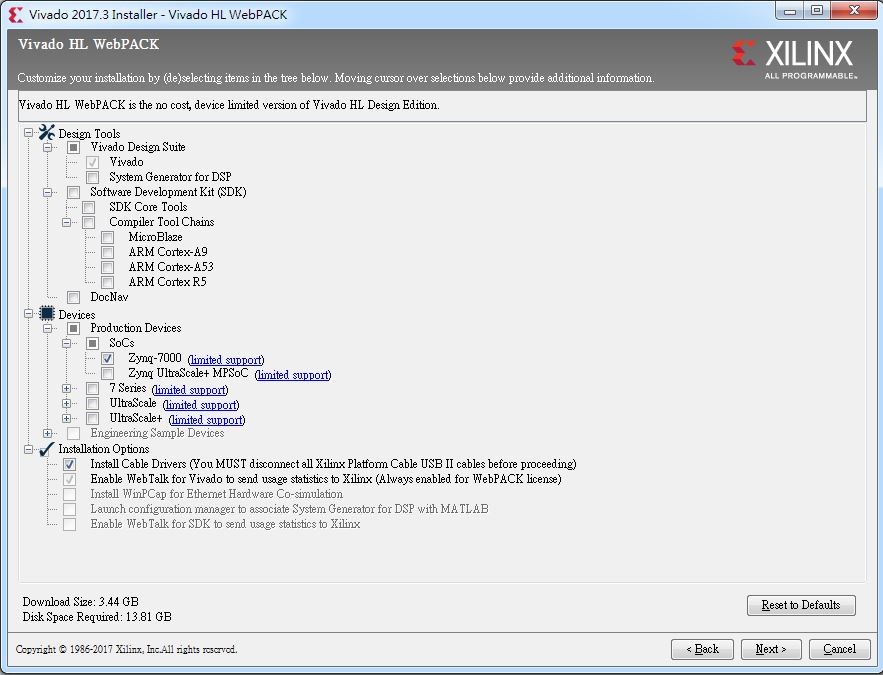

步驟二 下載完之後它是一個Vivado的下載器,點開之後原則上會遇到幾個問題,第一個就是要選哪種版本,那這邊我們就使用免費的版本,這版本對我們來說就足夠了,接下來第二個問題是要安裝哪些功能,那為了節省Vivado占用硬碟太大的空間,我們就安裝基本的功能就好,如附圖,剩下的都不用勾沒關係,之後就是漫長的等待了。

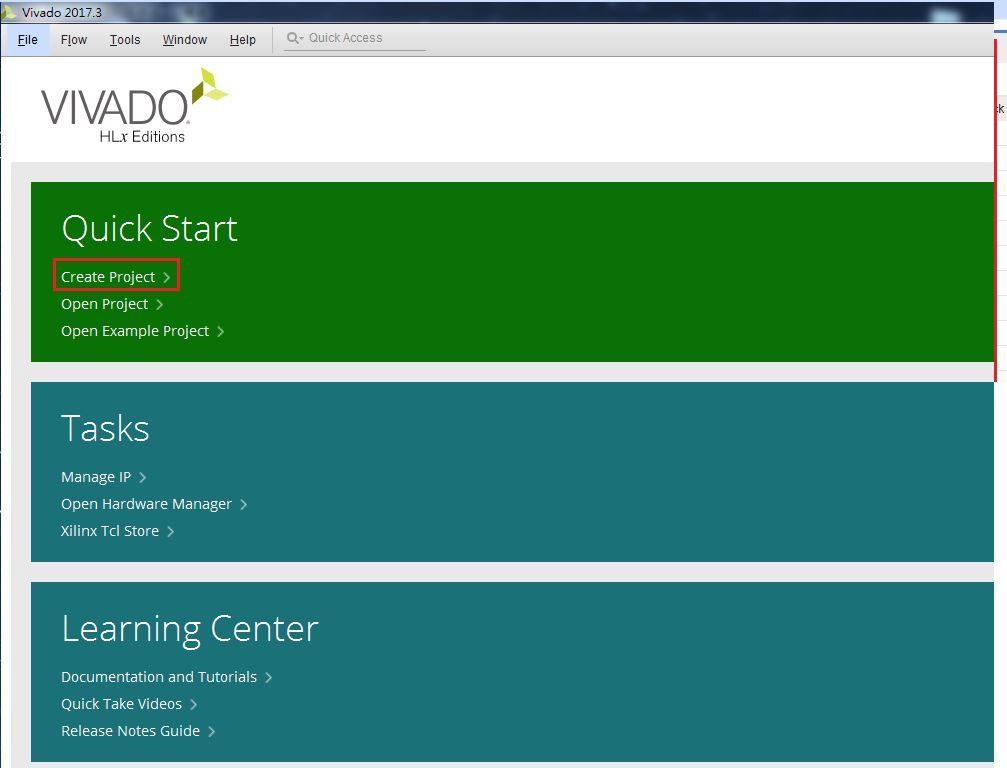

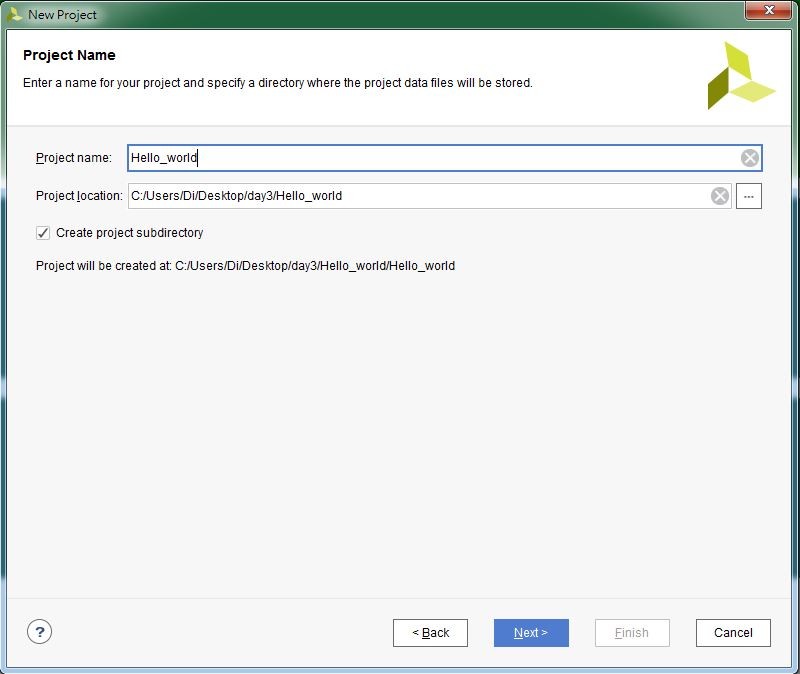

安裝完之後就可以來寫第一隻程式了,首先我們先創一個專案

打完專案名稱接著下一步

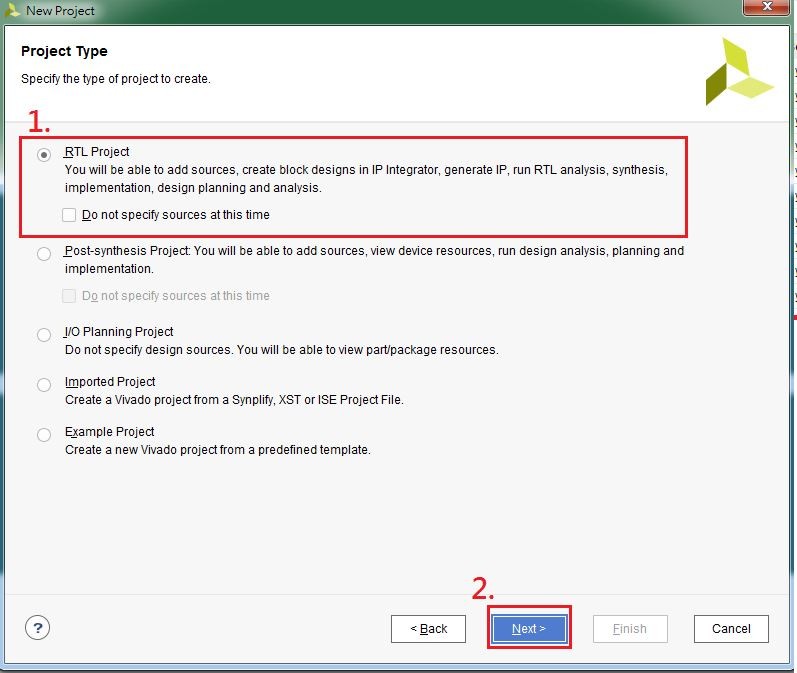

接著我們要寫verilog並且跑模擬,所以我們就選第一個選項,RTL(Register Transfer Language)。

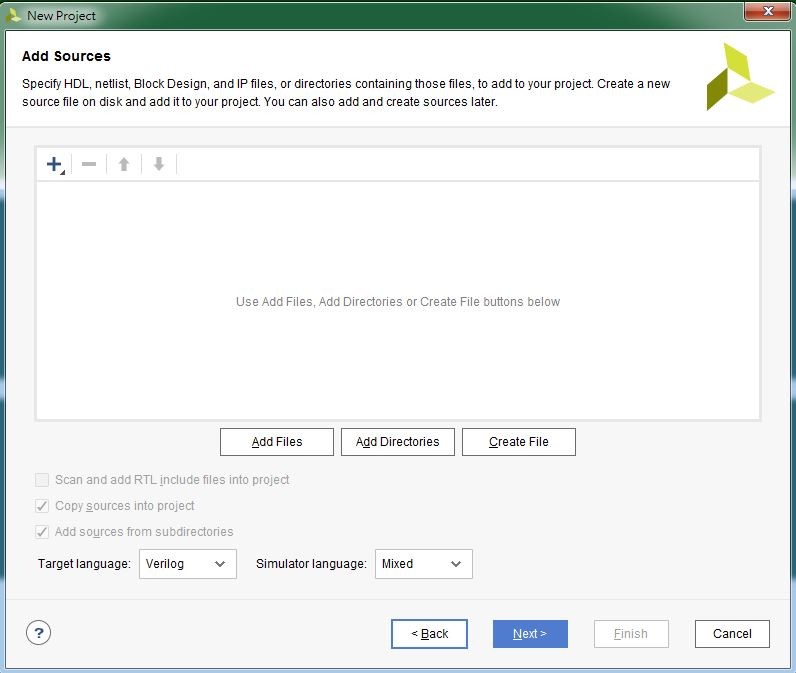

如果之前有寫好的verilog code可以在這邊include,沒有的話就下一步。

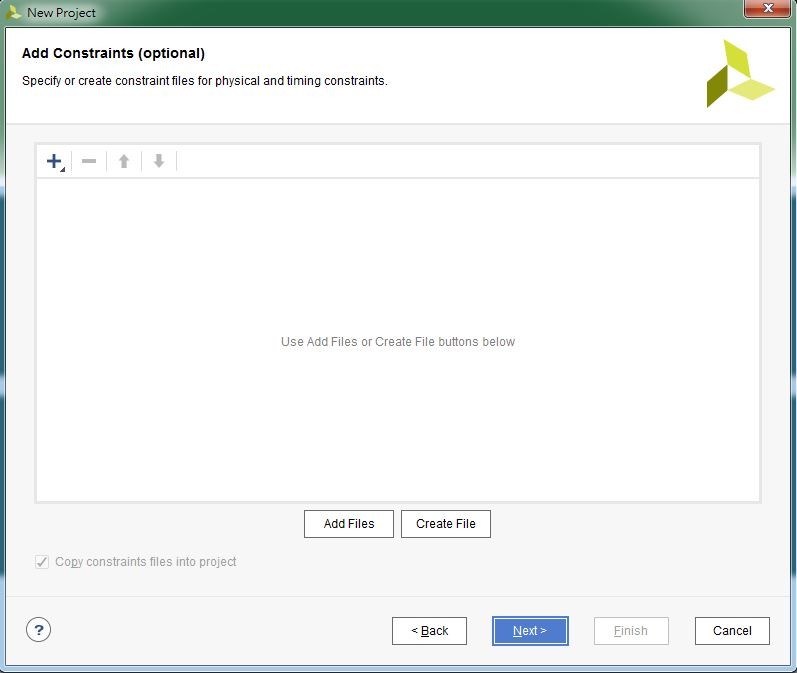

如果是要上FPGA板子的話,這邊是在include 板子的constrain file,constrain file內容包括對應的input output腳位 clock和 reset之類的宣告,目前用不到就直接下一步吧。

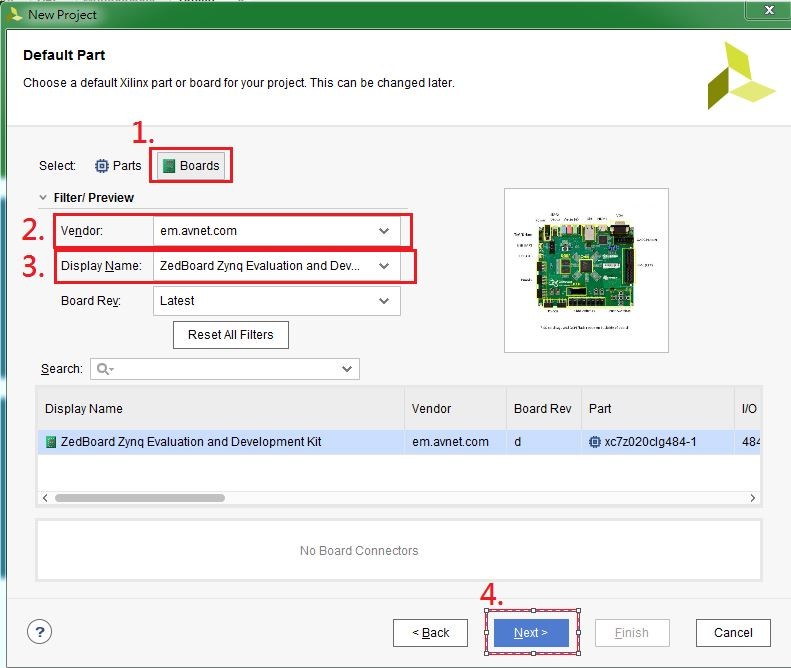

這邊是要選你要用哪塊板子實現你的電路,但目前我們這一列都只是驗證行為上的正確性,只要跑模擬就好,並不會在FPGA板上實際操作,所以板子可以任選沒有關係,那就照圖片的步驟往下做。

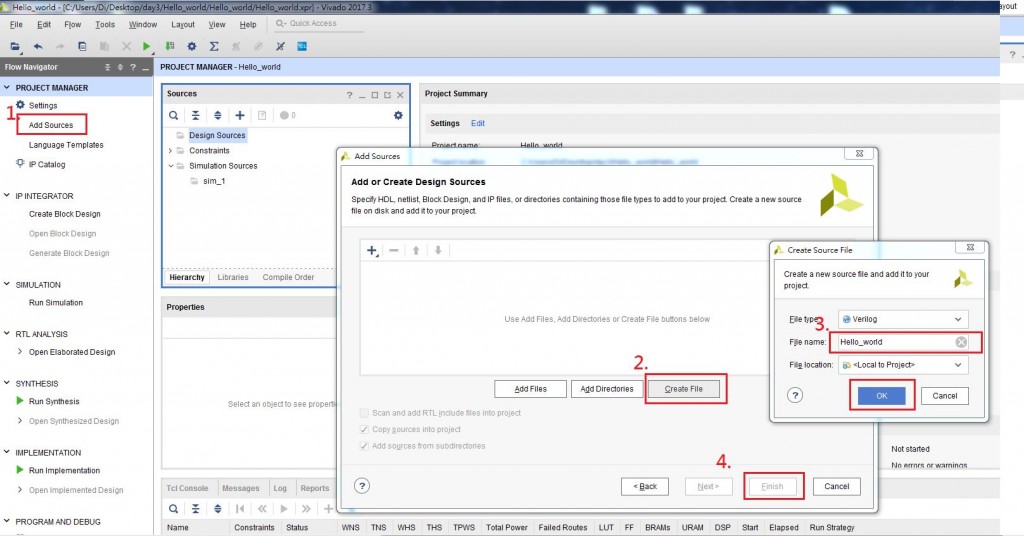

專案創完之後,需新增空的verilog(.v)檔,如附圖。

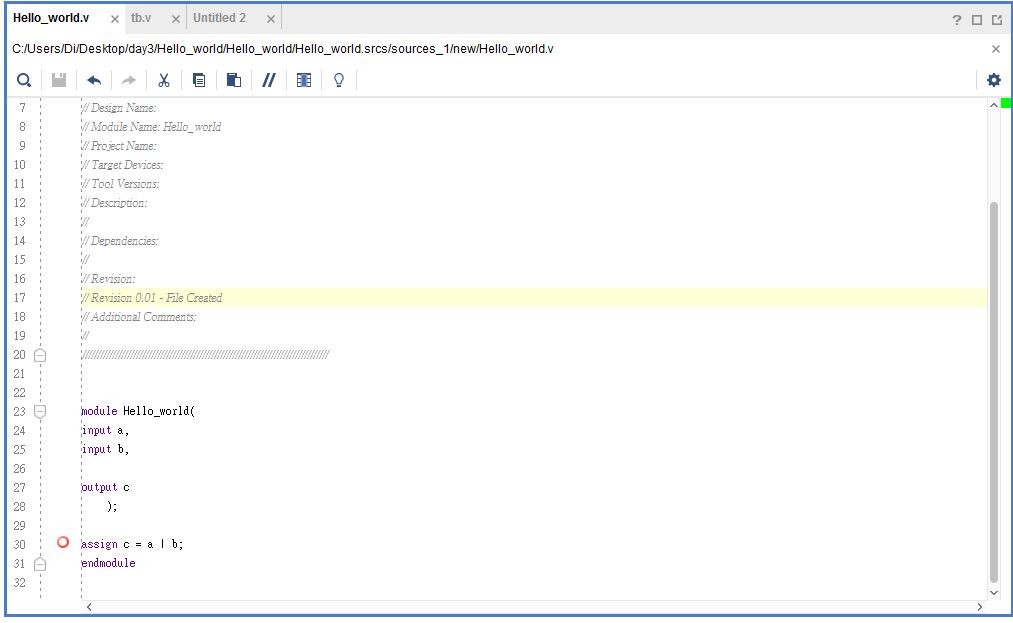

創完之後來寫一段簡單的小電路做測試。

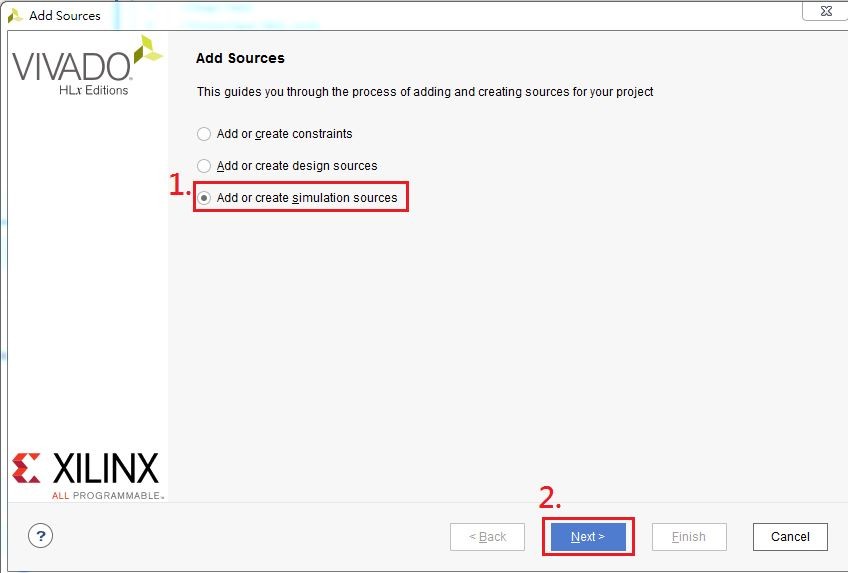

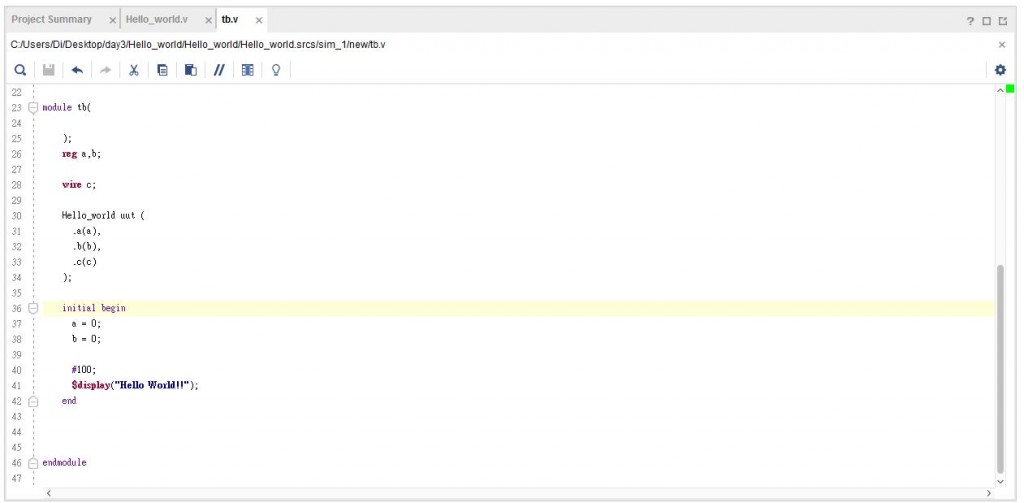

寫完之後來寫一個簡單的testbench,目前都只是測試tool是否運作正常,語法往後幾天會再跟大家分享。

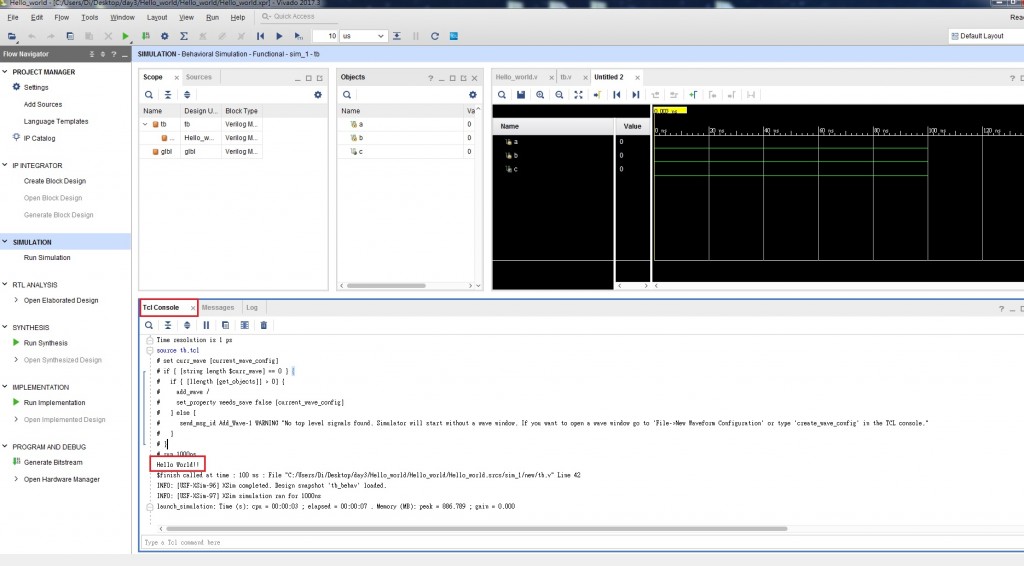

到了最後一個畫面代表使用上大致沒有問題,往後的操作不外乎就是以上這些動作,創一個專案,寫verilog code,寫testbench模擬電路是否正確,安裝過程中或著tool使用上如果有任何問題歡迎大家留言發問喔。