我們來講講一些數字的講法吧

比如說: 14 = 0x0E = { 4'b1110 }

4'b1110 就是 bin 的表示法

4是指 4個 bit ,然後分別是:

bit 3 = 1

bit 2 = 1

bit 1 = 1

bit 0 = 0

而 {} 就是連接運算子,可以連接多個運算元

舉個例子:

4'b1110 = { 2'b11 , 2'b10 }

在 verilog 中 我們可以用 assign來處理

再講一次: assign 輸出訊號 = 訊號跟運算子的組合

assign Out1 = { 2'b11 , 2'b10 } ;

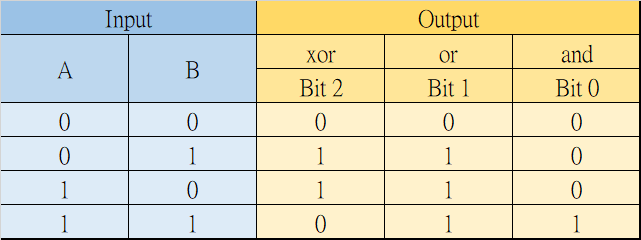

我們拿之前的程式改成 Out1 為向量的方式

module Test_gate1(A,B,Out1,Out2);

input A , B ;

output[2:0] Out1;

output[4:0] Out2;

and(Out1[0],A,B);

or(Out1[1],A,B);

xor(Out1[2],A,B);

assign Out2 = { A,B ,Out1 };

endmodule

tb為:

module tb1();

reg A_in , B_in;

wire[2:0] out_o1 ;

wire[4:0] out_o2;

Test_gate1 test(

.A(A_in),

.B(B_in),

.Out1(out_o1),

.Out2(out_o2)

);

initial

begin

A_in = 0 ;

B_in = 0 ;

# 100;

A_in = 1 ;

B_in = 0 ;

# 100;

A_in = 0 ;

B_in = 1 ;

# 100;

A_in = 1 ;

B_in = 1 ;

# 100;

end

endmodule

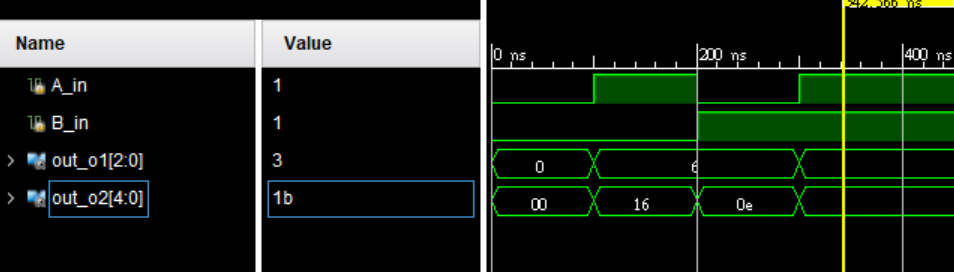

輸出結果:

可以比對一下

最近的步調放得有點慢,因為我覺得前面能夠理解比較重要

接下來會講 always

明天見~