大致認識了有限狀態機後,我們來試試透過 Verilog 實作出來吧!

我們先介紹一個 Verilog 的線上練習平台:HDLBits

這個平台包含了各式各樣的 Verilog 習題,從簡單的組合電路到進階的循序電路都有涵蓋

大家可以試試看喔!

今天,我們所要嘗試的是 HDLBits 中關於有限狀態機(FSM)的題目:

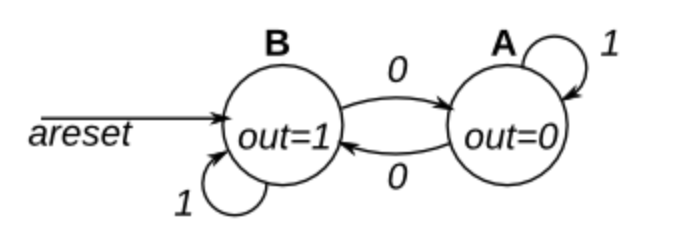

我們就單純從狀態變遷圖來了解狀態間的關係!

A = 0, B = 1。1, 0 ,不同的輸入搭配不同的狀態,可以得到不同輸出狀態B (特別注意使用的是非同步重置)撰寫程式碼時,我們可以將過程分成 3 個步驟:

module top_module(

input clk, in, areset, // Asynchronous reset to state B

output out);

parameter A=0, B=1;

reg state, next_state;

// State transition logic

// State flip-flops with asynchronous reset

// Output logic

endmodule

output out 輸出透過這三個步驟,也許你可以寫出正確的程式碼

module top_module(

input clk, in, areset, // Asynchronous reset to state B

output out);

parameter A=0, B=1;

reg state, next_state;

always @(*) begin

case (state)

A: next_state = in ? A : B;

B: next_state = in ? B : A;

endcase

end

always @(posedge clk, posedge areset) begin

if (areset) state <= B;

else state <= next_state;

end

assign out = (state == A) ? A : B;

endmodule

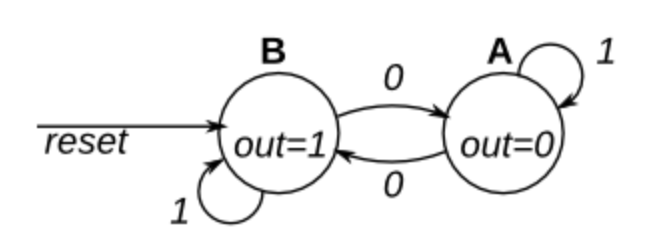

這題的邏輯和第一題一模一樣,唯一不同的地方是「同步重置」(synchronous reset)!

雖然題目長得幾乎一樣,但是程式碼的結構卻是差很多。

我們要非常清楚同步與非同步重置的差異,尤其是觸發時機,如果瞭解了其中的精神,這題可以說是迎刃而解啦~

// Note the Verilog-1995 module declaration syntax here:

module top_module(

input clk, reset, in,

output reg out

);

parameter A = 0, B = 1;

reg present_state, next_state;

always @(posedge clk) begin

if (reset)

present_state <= B;

else begin

case (present_state)

A: next_state = in ? A : B;

B: next_state = in ? B : A;

endcase

present_state = next_state;

end

end

assign out = present_state;

endmodule