這一章節要來認識CPU的組成,一切要回歸到設計的起點 ﹣馮紐曼模型 Von Neumann model(也稱范紐曼架構/馮紐曼模式),現在計算機的通用架構大部分都是基於它,主要精髓在於「儲存程式」的概念,由以下四大部分所購成:

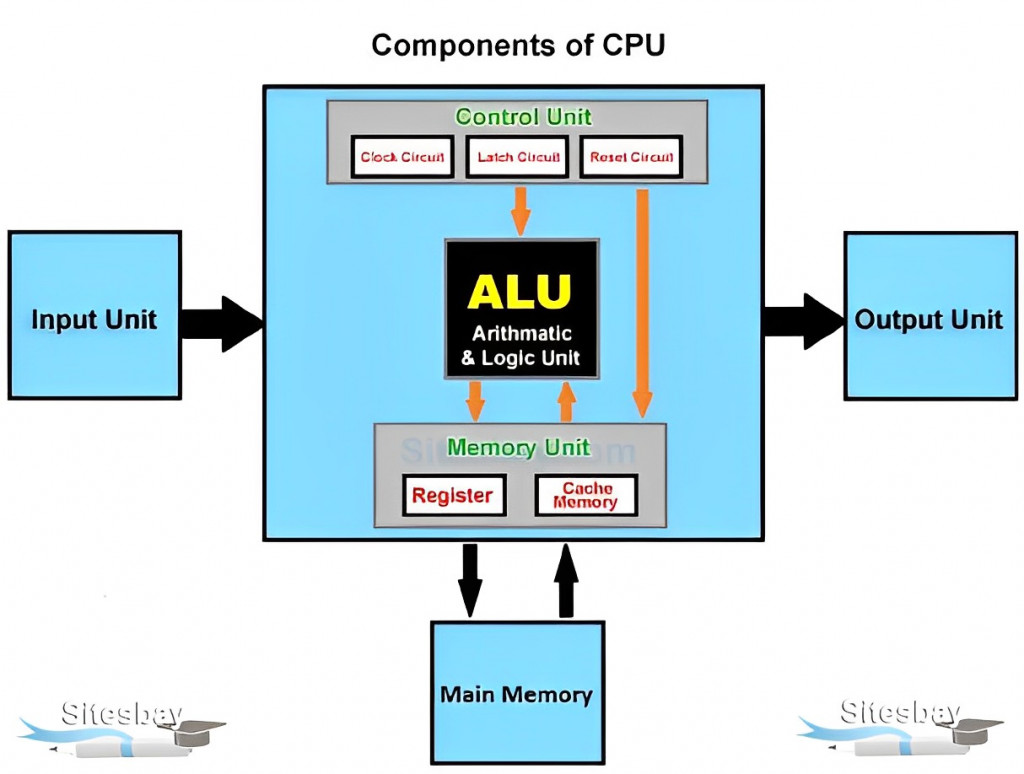

其中控制單元 + 算數邏輯單元 = 中央處理器 (CPU, Central Processing Unit)

圖片取自sitebay.com

CPU 是由以下幾個元件組成:

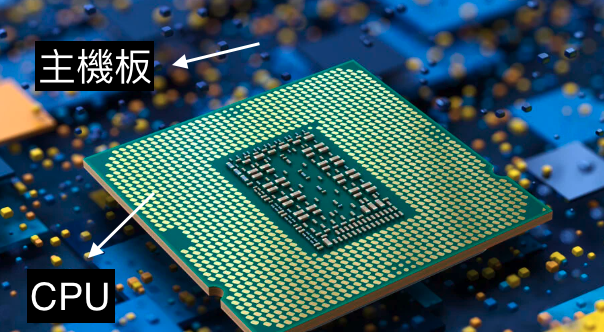

就像我們的大腦掌管著身體裡的所有運作,如血液循環和消化系統。處理器(CPU) 就如同電腦的大腦,用來執行存在記憶體的指令以及控制資料的處理、運算、儲存,它的外觀是一個晶片,位在主機板上,CPU 內部的每個元件都很重要,都有屬於自己的專屬的工作要做,電腦的效能好不好跟 CPU 也有著密不可分的關係

職責:指揮電腦執行程式的流程,控制記憶體,輸入/輸出、算數邏輯的運作

可以把控制單元想像成一位樂隊指揮,不必親自下去演奏!但要負責指揮各個區域的演奏者,如同負責指揮電腦各個系統單元間所要進行的任務,協調系統單元間的運作,例如:控制單元會從記憶體中將要執行的指令搬到暫存器並對指令解碼,然後交給算數邏輯單元運算,再將運算完的結果放回暫存器或是記憶體

欲執行的指令 ➜ 暫存器 ➜ 解碼 ➜ 算數邏輯單元運算 ➜ 結果(放在暫存器或記憶體)

算數邏輯單元(ALU) = 算數單元(AU) + 邏輯單元(LU)

職責:負責處理數字數據的運算(加減乘除)和邏輯,像是比較兩個數的大小, 產生亂數等

可以把算術邏輯單元想像成一位數學家,除了基本運算,也負責 AND、OR、XOR(eXclusive OR,兩者相同為 0、反之為 1 )、NOT、位元運算等邏輯運算。算數邏輯單元也擁有對 CPU、記憶體及輸入/輸出設備的直接讀入、讀出許可權

某些 CPU 會包含一個以上的 ALU,一個用來進行定點數操作(Fixed-Point Operations),另一個進行浮點數運算(Floating-Point Operations),如果有人好奇這兩者的差別,這裡直接附上 chatGPT 給我的回覆

算術邏輯單元是 CPU 中很關鍵的部分,因為它處理了大部分的數字計算和邏輯

X | Y | AND | OR | XOR

------------- | -------------

0 | 0 | 0 | 0 | 0

0 | 1 | 0 | 1 | 1

1 | 0 | 0 | 1 | 1

1 | 1 | 1 | 1 | 0

| X | NOT |

|---|---|

| 0 | 1 |

| 1 | 0 |

CPU中有一個極小的儲存裝置,稱為 「暫存器」(register),既然都叫暫存器了,顧名思義就是存放暫時性的指令、位址和任何類型資料的小倉庫,例如:位元組順序(Byte Order, Endianness)或是單個字符

暫存器的存取速度比主記憶體(RAM)快很多!因此,當 CPU 需要頻繁存取某個資料時,將它儲放在暫存器中可以提高效能,這樣處理器就不需要每次都從主記憶體中進行讀取、操作,可以直接從暫存器中獲取資料,有了這些臨時小倉庫,可以大大提升 CPU 的效能,在計算機執行複雜任務的同時,可以快速訪問和操作資料

就像倉庫有小、中、大、超大的差別,暫存器也有,常見的是以下幾種:

32 bit 和 64 bit 的暫存器是目前電腦比較常搭配的規格,這些數字代表暫存器的大小和寬度以及可以在單個操作中處理的資料量,在某些特殊架構中,像是向量處理、加密操作、大數據集,可能可以找到更大的暫存器,例如 128 bit、256 bit、甚至更大,這些較大的暫存器通常用於特定用途

暫存器有分很多種,像是 Data Reginster, Accumulator, Control Registers 等,其中講講兩種比較特殊的:

指令暫存器(Instruction Register, IR): 用於儲存當前正在執行的「指令」,從解碼、準備到執行完成的過程中都會被持續的儲存

程式計數暫存器/程式指標暫存器(Program Counter): 記錄當前正在執行的的指令「位址」,每當程式計數暫存器獲取了程式指令後,計數器就會將指令指標的值 + 1,接著就會指向序列中的下一條程式指令。當計算機重啟或重置時,程序計數器就會恢復為 0

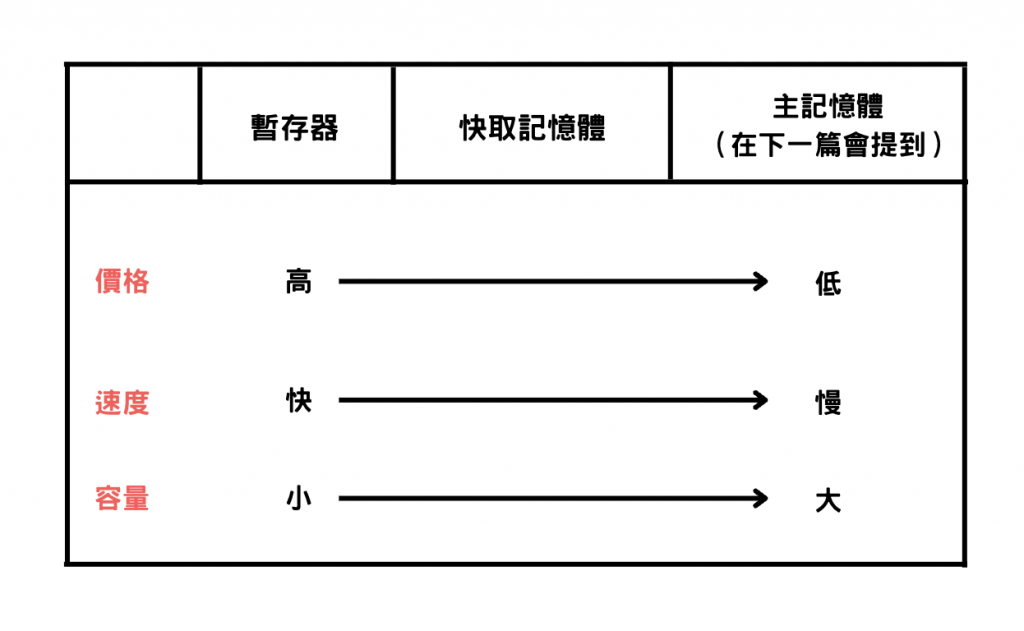

暫存器(Register)和快取(Cache)都是 CPU 中處理記憶體的單元(Memory Unit)

暫存器的速度最快,但價格也最高; 快取雖比暫存器的速度慢,但價格相對便宜,容量也比暫存器多很多,請看以下表格:

如果每次 CPU 在執行時,都要從主記憶體裡讀取資料,而主記憶體傳送到 CPU 的速度比較慢,效率就會大打折扣!不論 CPU 與記憶體的速度再快,也會受限於匯流排(下一篇會提到)的速度,這稱為馮紐曼頻頸(Von Neumann Bottleneck),為了解決這個問題,使用快取可以提高 CPU 與記憶體之間的頻寬。在實務上,可以把快取想像成一個透明部件,人類無法直接干涉對快取的操作,必須要去猜測哪些主記憶體的區段會被執行,先將這部分搬到快取,可想而知,如果猜測準確,執行效率就高,反之亦然!

Cache 能發揮其效用,主要是因為程式運行時對記憶體的存取展現出了局部性特徵,這種局部性包括「空間局部性」(Spatial Locality)和「時間局部性」(Temporal Locality)

當 CPU 發出記憶體存取的請求時,會先檢查快取內是否有請求的資料,如果有,則不經存取記憶體直接返回該資料;如果沒有,則要先把記憶體中的相應資料載入快取,再將其返回 CPU

PS. CPU 內部也有匯流排(bus),叫做「內部匯流排」,下一篇也會針對「匯流排」進行介紹

CPU 如同電腦的大腦,負責執行存在記憶體的指令以及控制資料的處理、運算、儲存。主要由控制單元 (CU)、算數邏輯單元 (ALU)、記憶體單元 (快取和暫存器) 所組成! 此外,目前大家所看到的電腦,都是基於「馮紐曼模型 Von Neumann model」(也稱范紐曼架構/馮紐曼模式),這對CPU的發展有極大的貢獻!在馮紐曼模式之前,電腦的運算程序都是使用「繞線方式」進行,換句話說就是我們在安裝軟體時,要使用一大堆線路,這會是怎麼樣的世界啊?![]()

PS. 若有解說不清或是不正確之處,歡迎指教![]()