今天要來介紹verilog的表示式以及運算元,verilog的表示式其實剛接觸時蠻令人霧煞煞的,所以想先來介紹一些表示式的用法,先來看一行給值的方法.

wire[31:0] temp;

assign temp = 32’d100;

這邊我是先宣告了一個32-bit型態為wire的變數

指定一個32-bit且為十進制值為100給temp

所以32’d100,32代表32bit,d代表十進制 100代表要給的值

所以一樣給100的值,也可以寫成以下形式

assign temp = 32’h64;(32bit 16進制)

assign temp = 32’h00000064;(前面的0可有可無)

assign temp = 32’b0000_0000_0000_0000_0000_0000_0110_0100;

上面都是表示要給十進制為一百的值給temp

給值的時候也能指定給特定的位置,像是:

assign temp[3:0] = 4’d7;

assign temp[7:4] = 4’b1010;

上面這行的意思是指定第3到第0個bit的值為7,第7到4個bit為10,也可以這樣寫:

assign temp = {4’b1010,4’d7};

用一個大括弧括起來,所表達的意思是一樣的,就看大家覺得哪個方便.

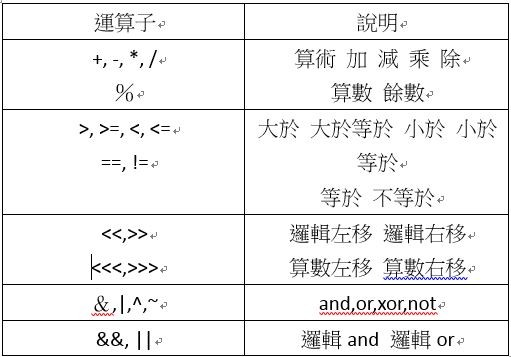

接下來要介紹運算子,一個一個講有點太冗長,所以直接整理一個表格給大家:

這邊的&跟&&可能比較會搞混,&比較像是and邏輯閘,可能把某幾個值用and閘and起來,&&比較屬於用在判斷條件上,像是if(c1 && c2)代表c1跟c2條件都成立時所要做的事情,某種程度上&也可以代替&&,所以像|跟||也是一樣的道理。

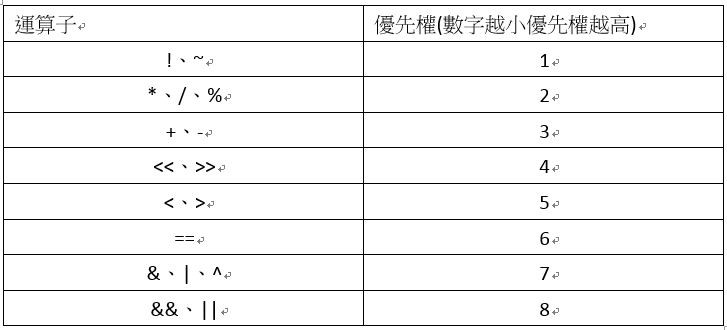

上面這表格是各個運算子的優先權整理,如果要用多個運算子的話要小心優先權大小並用多個括弧去搭配需要的電路。