前幾天大致上把語法介紹差不多了,會用到的大致上就那些,如果以後有用到一些比較特殊的語法會在介紹,或者說如果有讀者想要瞭解其他沒有介紹的語法也歡迎留言,我會在留言區介紹,又或者站內信給我也歡迎喔.

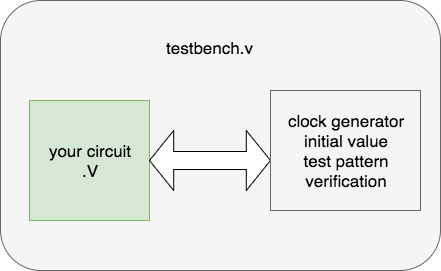

當你完成你的電路之後,要如何知道自己寫的對不對,不建議採用try and error的方法來debug,除了非常消耗時間以外,還會越嘗試越難過,所以今天要來介紹testbench,目的是用來驗證電路的正確性,首先先來看一下testbench所扮演的角色:

一個寫好的電路可能會用一個或數個module來呈現,所以在寫testbebch時,就是要產生input的訊號線的值給你的module,然後把output的值拿出來驗證正確性,今天大概會先介紹該怎麼去寫簡單的testbench,那我們直接開始吧.

我們沿用之前的加法器電路

module adder(

input clk,

input reset,

input [7:0]a,

input [7:0]b,

output reg[7:0]c

);

always@(posedge clk)begin

if(reset)

c <= 0;

else

c <= a + b;

end

endmodule

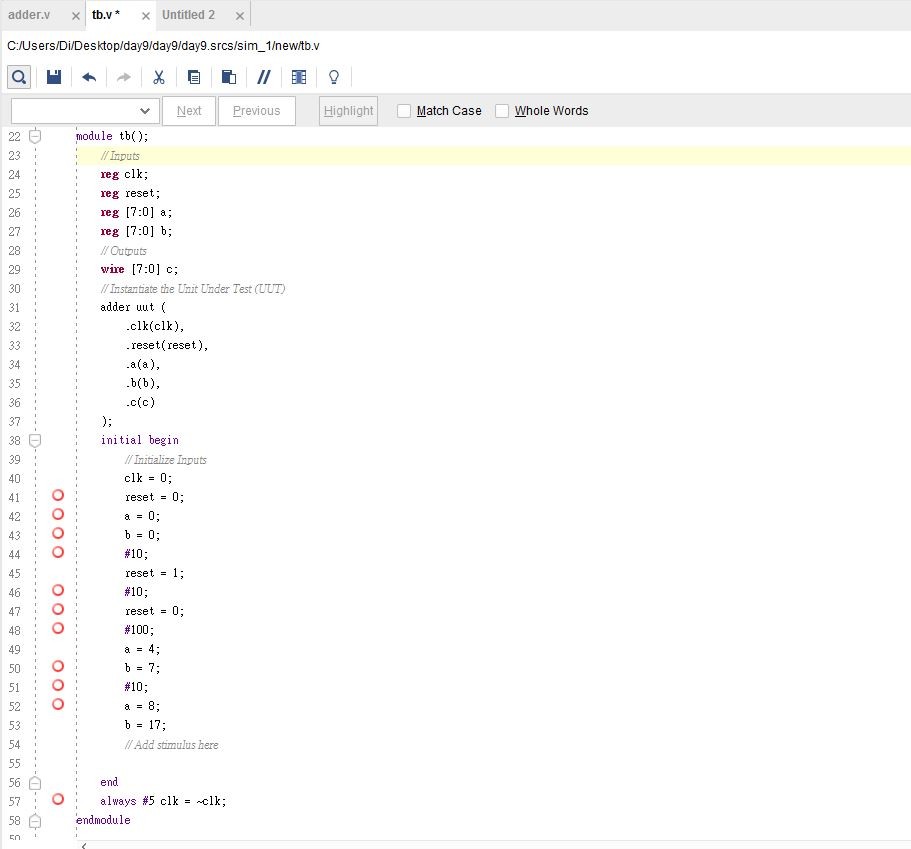

下圖為加法器的testbench:

那現在來對testbench一行一行做解釋吧,

首先line.22是testbench的名稱,因為沒有input output所以括弧內沒東西,

line.24開始是宣告你要接到你的module的訊號線,這邊要注意的是接進去的訊號線為input的話,要宣告為reg形態,反之,如果是output的話,宣告要為wire.

line.31這邊就是在宣告你的module,有點像是include的概念,所以這邊我宣告一個adder(我要測試的module名稱)名字為uut,名字取什麼都可以,然後把要接進去或拉出來的input,output設定好,舉例來說line.32的.clk(clk),左邊的clk是adder裡面宣告input的clk,而括弧內的clk為testbench所產生的clk,然後要把這兩條訊號線串接起來的意思,這樣說明應該比較好理解.

line.38的initial begin end在這裡面的block就是要做驗證電路的pattern,這裡面寫的方式就像c code一樣,在模擬的時候是由上往下一行一行執行,以這邊來說明一下,通常我在寫的時候都會先把input歸零,就像line.40到line.43,

之後把電路做reset功能line.44到line.47,中間#10 代表過了幾個單位時間,這邊來說一單位時間為1ns,接下來就可以開始寫你要給的測資(line.48到line.54).

最後line.57.是產生一個clock,每當5單位時間就做反向,以這邊的話就是產生100MHz的clock,一個單位時間為5ns.

這樣就完成一個簡單的testbench,實際來跑一次吧.

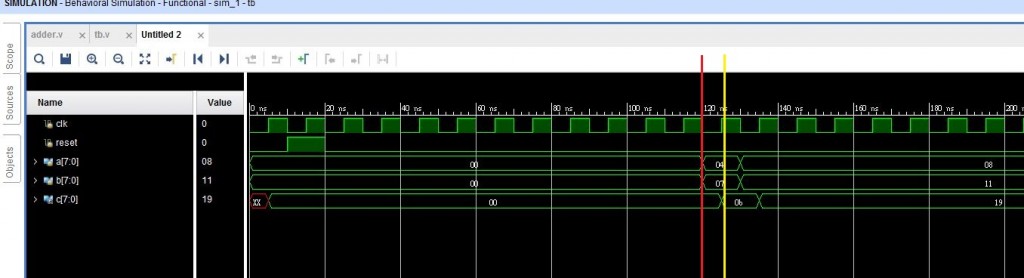

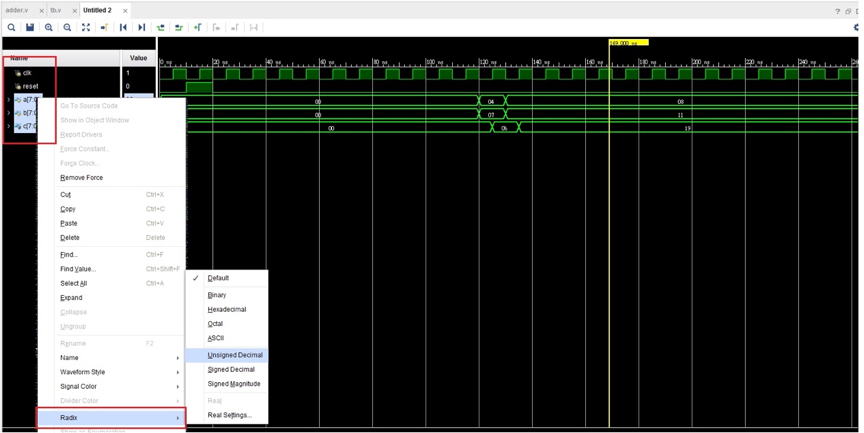

跑出來的結果如上圖,電路剛開始所有input都會歸零,過10ns個做reset,然後看一下紅線的部分,是給第一筆測試資料(a=4,b=7),至於黃色線部分是給完第一筆資料所產生的結果(c=0b),並給下一筆新的資料(a=8,b=11),之後下一個正緣觸發產生新的結果值(c=19),上面所說的直都是16進制,如果要改進制的話可以參考下圖.

今天大概介紹testbench的一部份,接下來會再花個一兩天介紹.

協助勘誤

原文: 不建議採用try and error的方法來debug

建議修改: 不建議採用trial and error的方法來debug