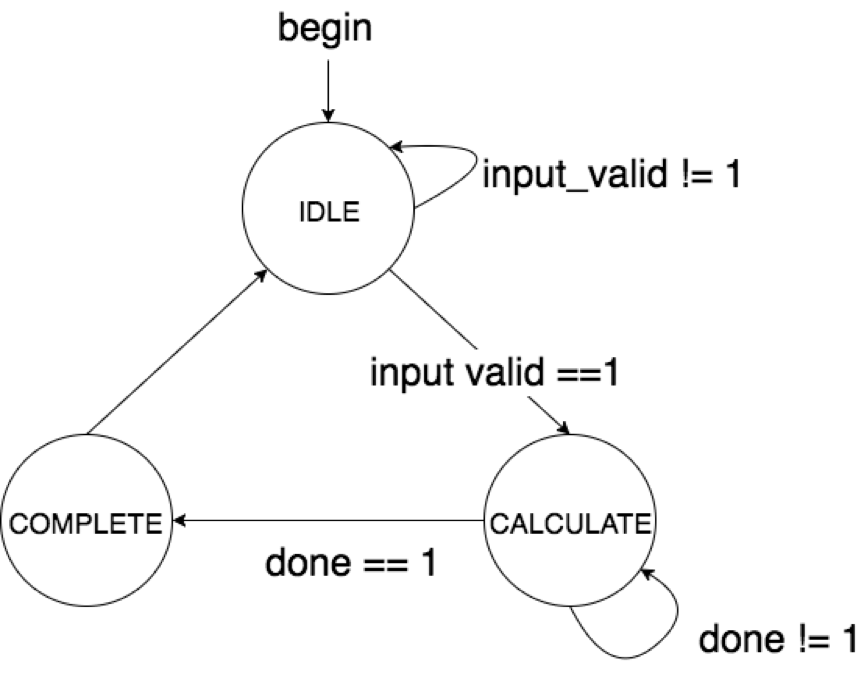

今天要來介紹 有限狀態機(Finite State Machine) 簡稱FSM,為什麼要介紹這個呢,因為FSM在verilog扮演一個非常重要的角色,當你在寫verilog時,且是一個較為複雜的電路時,你要如何去控制每個always block裡面的行為,或許你可以設很多的flag,哪個flag觸發就做指定的行為,但這樣或許就會造成程式的可讀性降低,或者是當電路有bug時,就比較不好發現bug在哪,所以在寫較為複雜的電路時,大多人都會用FSM來控制電路行為,在哪一個狀態該做哪些事情,其他狀態就保持不變,一來可讀性增加,二來降低電路的複雜性,所以把FSM推薦給大家,那接下來先來介紹一下什麼是FSM.

首先來看一下FSM程式的模型

always @(posedge clk)begin

if(reset)

FSM_STATE <= IDLE;

Else

FSM_STATE <= FSM_STATE_NEXT;

end

always@(*)begin

case(FSM_STATE)

IDLE:

if(in_valid) FSM_STATE_NEXT = CALCULATE;

else FSM_STATE_NEXT = IDLE;

CALCUALTE:

if(done) FSM_STATE_NEXT = COMPLETE;

else FSM_STATE_NEXT = CALCULATE;

COMPLETE:

FSM_STATE_NEXT = IDLE;

default:FSM_STATE_NEXT = IDLE;

endcase

end

大概解釋一下,以上面的FSM來說會在電路reset的時候從IDLE這個state開始,然後等待input訊號進來,如果沒有input訊號的話就會一直停在IDLE,一旦有input訊號進來,就跳到CALCULATE state,等待電路運算完之後就會跳到COMPLETE做輸出,輸出完就能回到IDLE等待下筆input進來,大致上是這樣.

以上面這個簡單的範例大概能看出FSM的許多優點,讓程式表達非常明確,哪一個state該做什麼事情,明天會舉一個簡單的應用在加深各位多FSM的印象,那今天就先到這裡囉,謝謝各位.