今天要繼續昨天的主題,也就是blocking跟nonblocking介紹,今天多加一個元素,就是clock,大家應該會好奇如果把clock跟blocking&nonblocking融合電路會長什麼樣子,所以今天把這元素加進去分享給大家,好讓大家對verilog有更多的瞭解.

先來看一段類似昨天的程式碼

always @(posedge clk)begin

A1 = IN;

A2 = A1;

A3 = A2;

end

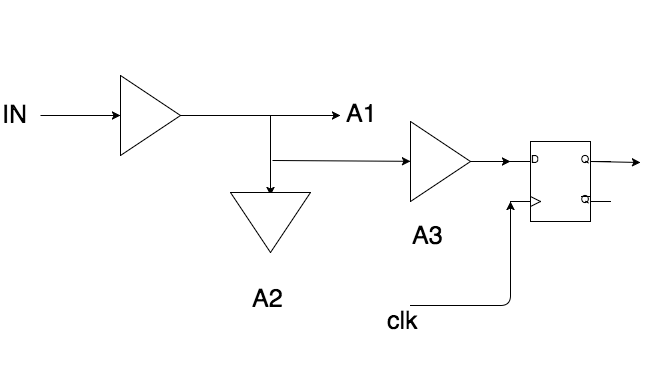

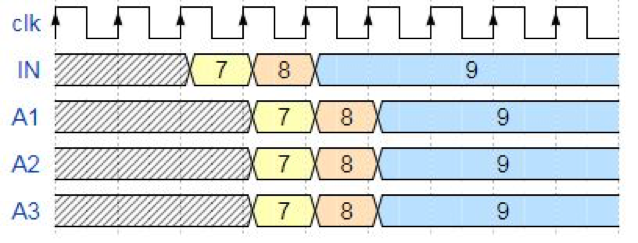

多加一個clock進去之後整個就會不一樣囉,來看一下電路及波形:

這樣就會隨著clock觸發描述行為,一樣是blocking的用法,但是就會變成循序邏輯電路的blocking,順便幫大家複習循序邏輯.

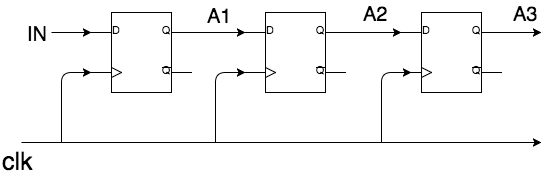

再來介紹 nonblocking(<=),所有用這種給值的方法在執行的時候都是同時給值的,意思就是在給值的時候不會有先後順序,都是依照當下那個clock上升的那瞬間的值去做決定,用講的比較抽象,還是一樣,畫個電路及波形來幫助大家加深印象.

首先來看一下程式:

always @(posedge clk)begin

A1 <= IN;

A2 <= A1;

A3 <= A2;

end

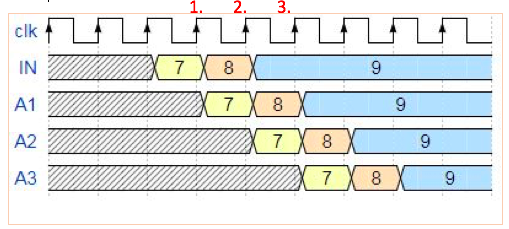

所以當IN有值時,第一個clock A1發現IN為7,然後就把7存以來,但這clock上緣瞬間A1值還是0,所以A2維持不變,A3也是,

等到第二個clock,A1發現IN為,所以把8存起來,這時候A2發現A1值為7,所以就把7存到A2裡面,但次時A2值仍為0,所以A3值仍不變,以此類推下去,也許解釋的不是很好,但是搭配波形圖看應該非常的清楚.

大家應該對blocking跟nonblocking之間的關係有進一步的瞭解了吧,提醒大家一下,在同一個always block裡面只能選一種給值的方式,意思就是blocking跟nonblocking只能選一種用,不能混用,不然就會有error的訊息出現,那今天就到這邊囉,謝謝大家.