今天要繼續來跟大家分享testbench的相關寫法,相信大家應該對testbench有一定瞭解了,但如果要驗證較複雜的電路,testbench也要設計得更完善,那今天我們簡單設計一個8bit-ALU如下,規格如下

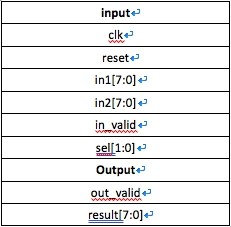

兩個8bit的輸入,sel為0時做加法,1時做減法,2時做乘法,3時做除法,並在in_valid為1的時候input才有效,算完的時候需把out_valid設為1,result才算有效,大致上是這樣,今天重點還是著重在於testbench,所以alu電路部分大家有興趣可以照著要求自己寫看看,那接下來繼續開始分享一些昨天沒介紹的testbench語法.

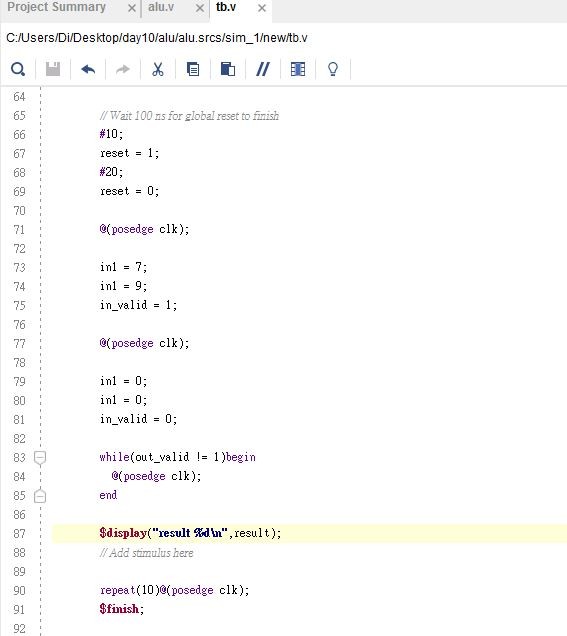

昨天提過的今天就不重複提了,line.71前就是昨天做的事情,包括宣告會用到的訊號線,把testbench所產生的input,output的線接進去拉出來,以及input歸零跟做reset的動作.

現在我們就直接從line.71開始吧,之前有提過,testbench 裡面的initial begin就像C code,是由上往下執行的,如果寫#10;就代表過了10個單位時間再繼續往下做下去,

那line.71代表的意思就是經過一個clock正緣觸發的時間之後再往下執行,

接下來line.83到line.85會一直偵測out_valid是不是等於1,不是的話就一直執行一個cycle的時間.

line.87就像C code的printf,可以把你想印的東西印出來.

line.90就是重複過了10個cycle,line.91是結束testbench.

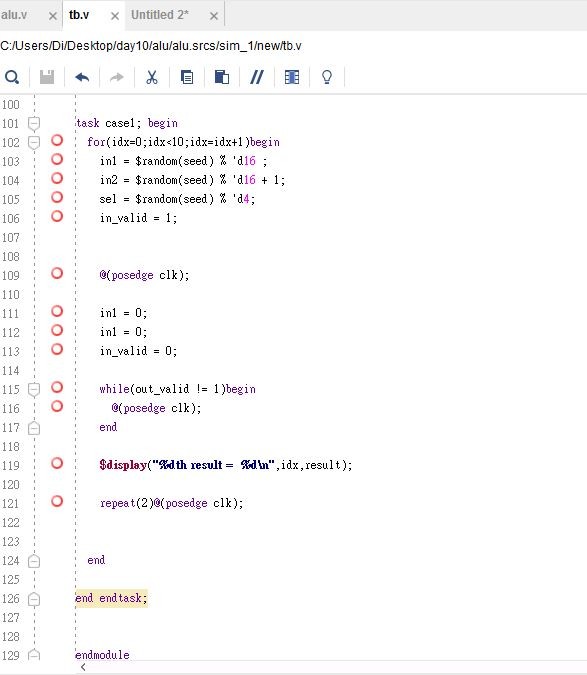

一個規模較大的電路可能要用不同組的測資去模擬,如果全部擠在一起的話可能就不方便閱讀,所以這邊在介紹一個方法如下圖.

這邊是把你要測試的pattern利用task包起來,然後再initail 的block中適時的呼叫它,大家可以參考一下上圖task的的描述,line.101到line.126,input的值都是用random的方式去產生,然後再for loop裡面連續執行十次,這邊的for loop就是像C code的for loop,一個迴圈一個迴圈執行,而不是像verilog會做展開並一次執行,接下來我就以幾張跑完testbench後所產生的波形圖給大家看.

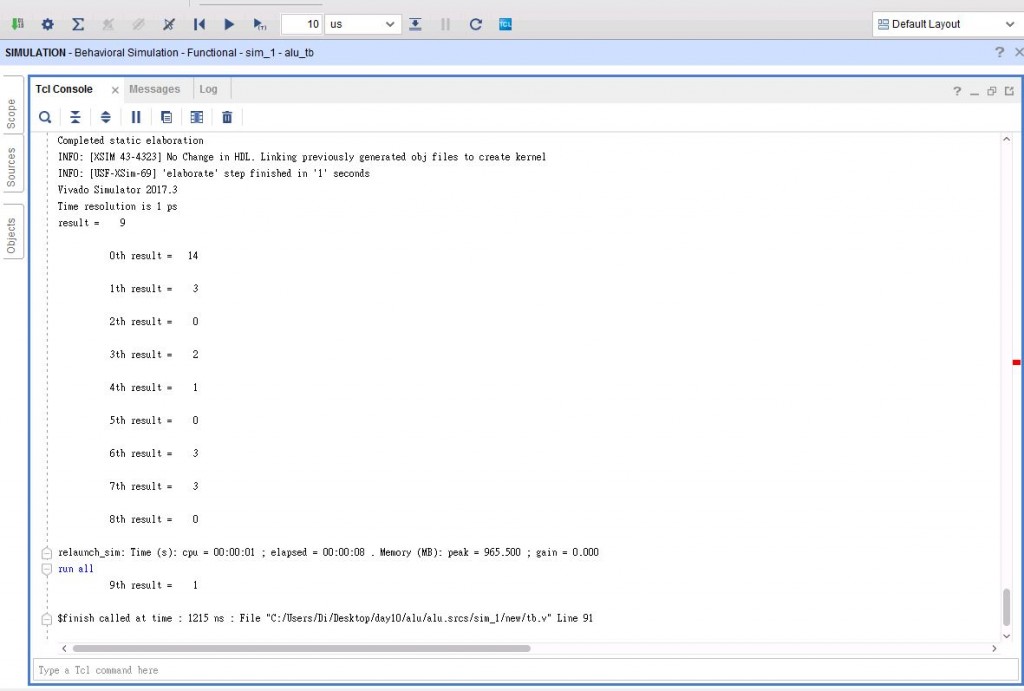

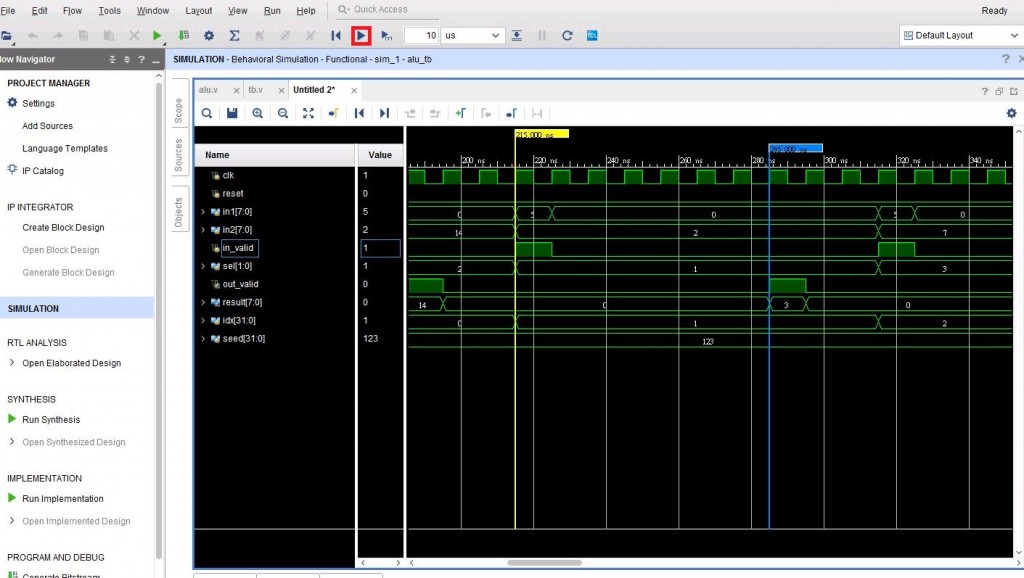

首先我們先來看我們印的東西,這邊會看到我們剛剛印的result,發現象印到8th有停一下是因為說,simulation預設模擬時間為1000個單位時間,這邊的話就是1000ns,所以你如果要讓他跑完你的模擬的話要按一個類似播放鍵的按鈕,如下

按完之後就會一直跑,跑到你設定$finish的地方,那從上圖得知當invalid=1時(黃線)我的alu就會開始運算,等運算完會發出out_valid=1的訊號(如藍線),然後過兩個cycle之後會再送下一筆要測試的資料到alu裡面直到finish結束.

今天就先到這裡囉,明天會再跟大家分享testbench最後的部分.