今天要來幫testbench做結尾拉,把一些常用沒有提到的功能在分享一下,然後後面會跟大家說一下一個完整的testbench該怎麼下手.

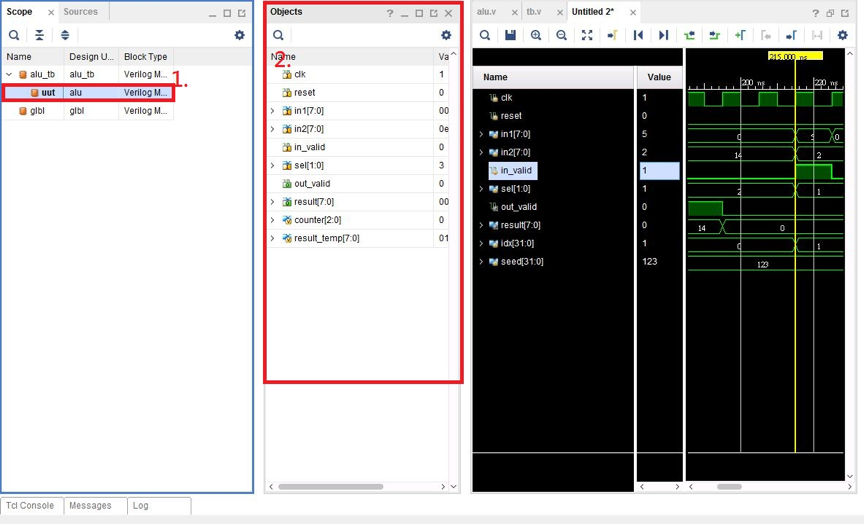

前兩天在跑模擬的時候,波形圖只會顯示input跟output腳位,但其實也可以把你電路有宣告的任何訊號線都可以抓出來看,抓的方式如下圖

照上面步驟,uut為宣告要測試電路的名字,點一下就會出現全部用到的訊號線,把你要看的訊號線按住左鍵拉到旁邊黑色的地方之後,按一下播放鍵右邊的一顆按鈕(relaunch)有點像重新整理,之後就能重新跑了.

再來是在寫testbench時,我們是判斷說ouput的接腳out_valid等於一去檢查答案,不過其實不一定要接到output腳位才能拿來做判斷,意思是只要出現在你的電路過的變數都可以拿來判斷,以這邊的例子,我在電路裡面有一個counter的變數,它不是output的形式,但是你可以利用以下方法:

while(uut.counter != 7)begin

@(posedge clk);

end

uut就是你在testbench所要測試的電路宣告的名稱,後面就是你的變數,有點像物件導向的感覺,所以寫testbench其實還蠻方便的.

訊號線的型態約分為有四個型態

1:高電位(綠色)

0:低電位(綠色)

Z:高阻抗(藍色)

X:unknown(紅色)

前兩個可能比較沒問題,Z的情況比較像是訊號線沒有接好造成開路,X的情況可能也有很多種,有可能是一開始沒有reset,或者沒有給初始值,如果遇到這種情況要一層一層去推問題在哪裡,因為假設一開始訊號線就是X的情況下,你拿X的值去assign給別條線,那被assign的訊號線也會是X,所以要一層一層推回去看是哪邊出了問題.

Testbench比較常用的功能就介紹到這,接下來來討論如何寫一個完整的testbench,一開始寫的時候你可以隨便寫一組測資就看波形大略看一下電路的正確性,比較常遇到問題的case往往在邊界或是比較特殊case的部分,像是邊界會不會遇到overflow,或者是除0的case這都是要考慮的部分,真正完整的testbench其實是非常麻煩的,難度不會輸給電路設計,以8-bit ALU來說,應該把加減乘除四種全部所有的可能都測過一次,意思是兩個input必須從0~255不斷的去做測試,然後要測加減乘除四組,所以要測2552554次,每一組測出來就去看一下結果是不是正確的.

所以越複雜的電路的testbench就越難設計,因為full case不是那麼好產生,所以其中的一個方法就是不斷用random去產生測資,但有一定的機率有些case是測試不到的,所以越好的testbench就是能測到越完整的case,所以大家在寫電路的同時不仿也可以想想有什麼特殊的case是需要多多去注意的,就可以避免掉不可預期的錯誤,那即使遇到問題也不要氣餒,波形一步一步推回去就那知道錯在哪裡囉.