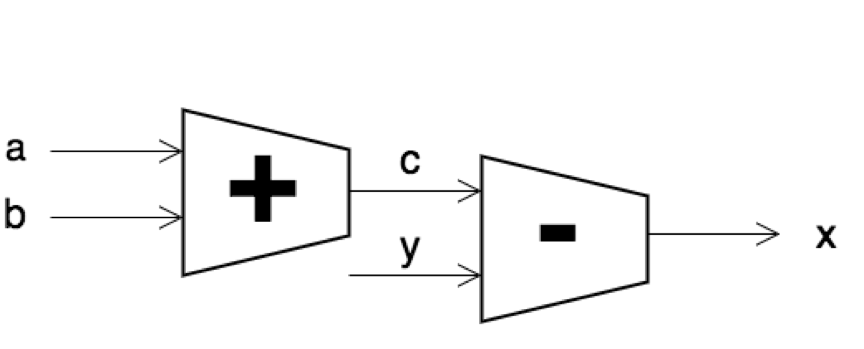

今天要來介紹之前所提過的 組合邏輯電路(Combinational Circuits) ,先來看看什麼是組合邏輯電路,參考一下下圖:

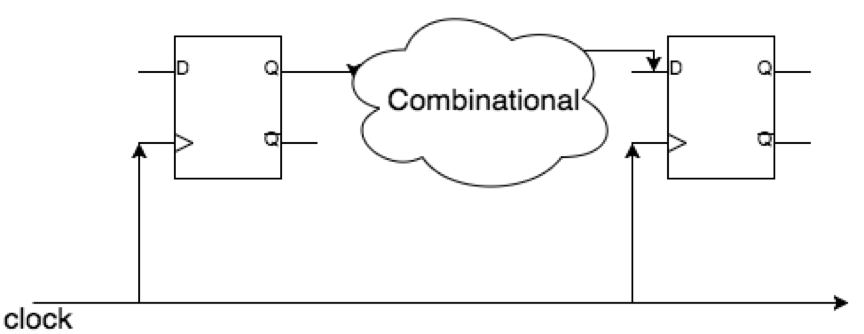

這邊可以看到圖中,一個完整的電路會拆成循序邏輯電路(將在明天介紹)一個是組合邏輯電路就是根據目前的input值產生對應的output值,之間不受clock影響,行為描述上用always block 或者是assign的方法都可以

always:

always@(*)begin

c = a + b;

x = c – y;

end

assign:

assign c = a + b;

assign x = c – y;

上面這兩個都是組合邏輯電路,而描述的意思也是做相同的事情,差別在於如果是用always做組合邏輯的話要宣告為reg,assign的話就要用wire去宣告,所產生的電路如下