今天要來講一下verilog兩種不同的給值的方式,分別為blocking & nonblocking,這兩種給值的方式經常讓剛學verilog的人很頭痛,當初我也是花了好一段時間再看,因為先學c的人再給值的時候很習慣用“=”,而不是“<=”,今天就來看看這兩者的差異吧.

首先來看一下blocking的方法,也就是在always block裡面給值的時候是用”=”的方式,假設你的給值是有相依關係,就像是a=b,c=a,d=c,那給值的時候就會按照你程式打的先後順序去執行,來按看一下例子

假設我設計了一段程式如下:

always @(*)begin

A1 = IN;

A2 = A1;

A3 = A2;

end

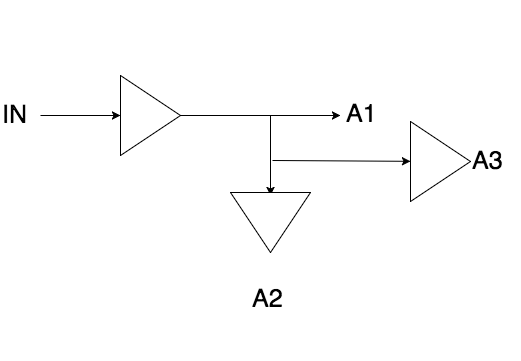

那麼就是當IN值改變的時候會觸發這個always運作,因為有相依性,所以會一行一行由上往下執行這block,出來的電路大概會長這樣:

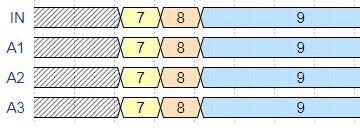

IN先給A1之後,再把A1給A2,最後再把A2給A3,模擬跑出來的波形大概會在以下這樣,因為跑模擬預設是邏輯閘之間是沒有delay的,所以當IN值改變時,其他值就都會改變

再舉一個例子:

always @(*)begin

A1 = IN+1;

A2 = A1+2;

A3 = A2+3;

end

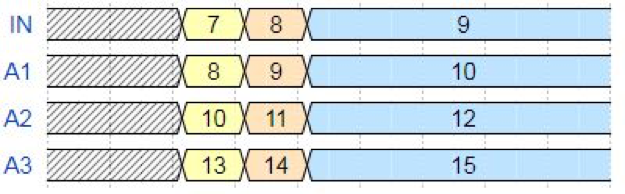

把上面的程式加一個加法器進去,波形就會長以下這樣

這樣搭配著波形以及電路看是不是有比較好懂了呢,明天會再繼續提nonblocking的部分,然後兩者之間再來做比較.