今天要來跟大家分享電路的儲存裝置,一個是Latch,一個是Flip-Flop,

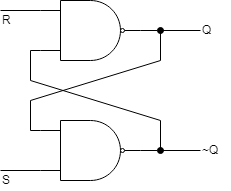

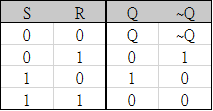

首先給大家看一下一個位元Latch的電路圖以及真值表,有學過數位邏輯的應該都有看過,不過還是簡單介紹一下,S是set,R是reset,所以當S跟R都為0時輸出值是不會變的,可參考真值表,所以這樣的電路為一個儲存元件.

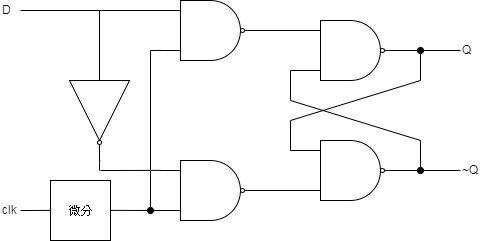

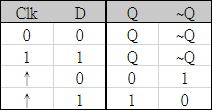

再來是Flip-Flop,看電路能發現比Latch多了幾個邏輯閘跟微分電路,下面這電路也稱D型正反器,輸入接腳為D(Data)跟clk(clock),意思是當clock正緣時才去觸發這個正反器,clk等於1跟等於0時值是不會變的,如真值表.

為什麼要介紹儲存元間呢,一方面加深大家寫電路的印象及對儲存元件的瞭解,一方面是要來講一下Latch在寫verilog時會造成的問題,因為實際在跑電路時,可能會有一些因素造成電路有雜訊的問題,造成如果使用Latch來儲存的話,可能會造成一些訊號誤判造成電路錯誤的情況,而Flip-Flop比較沒有這情況是因為只有在時脈上升的才改變值,所以時脈之間有雜訊並不會影響輸出值,所以今天要跟大家分享如何避免Latch的產生.

通常在寫combinational電路時才會出現Latch,而且通常是判斷條件沒寫完整的關係,會產生的原因大約為一下幾個

-if and else

always@(*)begin

if(rst)

a = 0;

else if(c1)

a = in1;

end

像以上這樣,所以要嘛把條件寫滿,或者給初始值,各舉一個例子

條件寫滿:

always@(*)begin

if(rst)

a = 0;

else if(c1)

a = in1;

else

a = 0;

end

補初始值:

always@(*)begin

a = 0;

if(rst)

a = 0;

else if(c1)

a = in1;

end

-case:

在寫case時,當case沒寫完整時,記得捕default:,不然也會產生Latch.

always@(*)begin

case(Q)

0:Q_NEXT = 1;

1:Q_NEXT = 2;

default:NEXT = 0;

endcase

end

-回授

通常也是在組合語言出現,自己給自己值,這樣就會產生Latch把值存起來.

assign a = a + 1;

always@(*)begin

a = a + 1;

end

會產生Latch情況大概就上面那幾項,大家在寫組合語言時要多小心,尤其是有判斷式時,要記得把情況寫滿或給初始值,但如果是循序邏輯的話就沒有這問題了,這邊就提供給大家做參考.